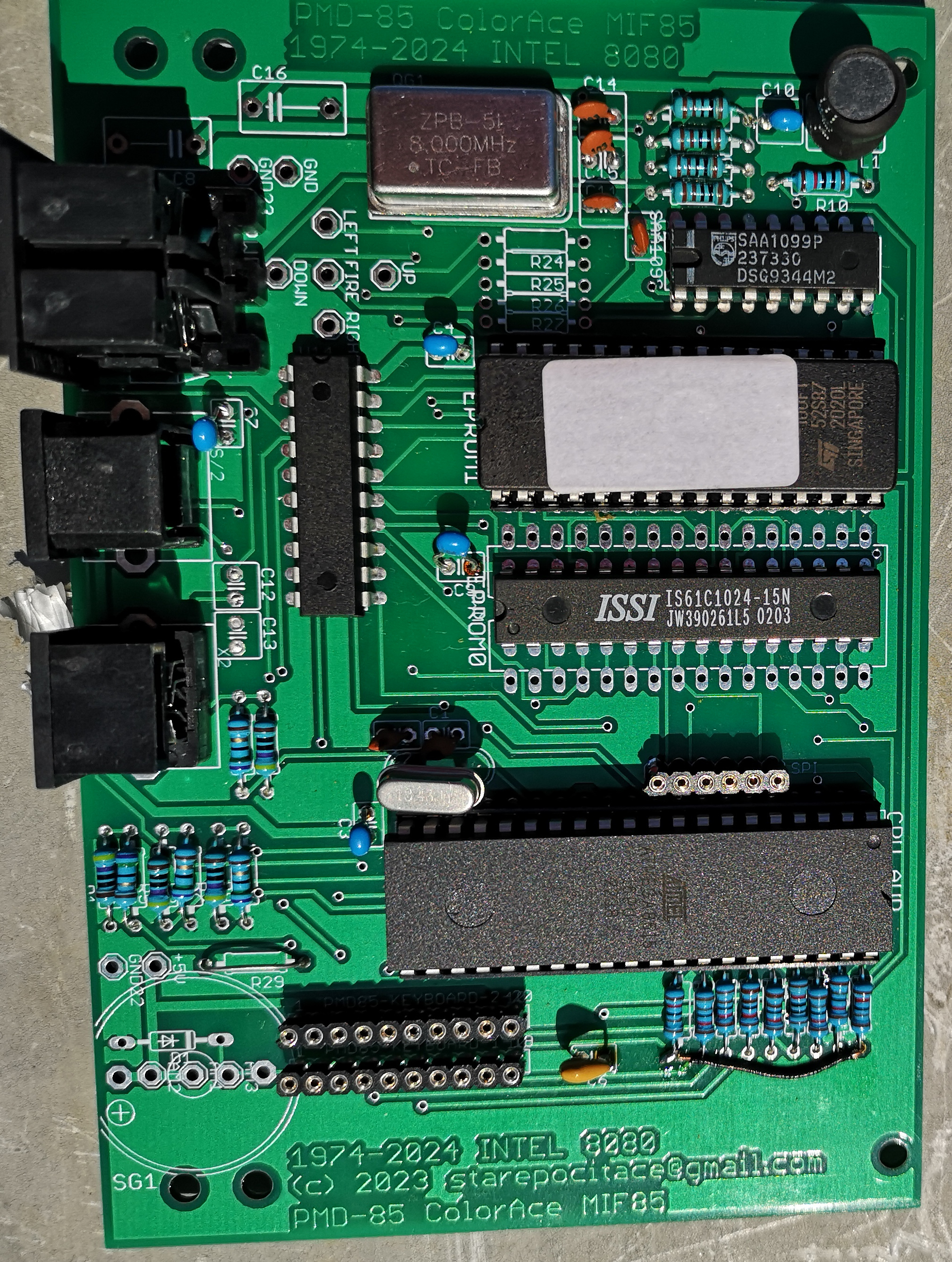

PMD-85 verzia MIF85 + colorAce 2023

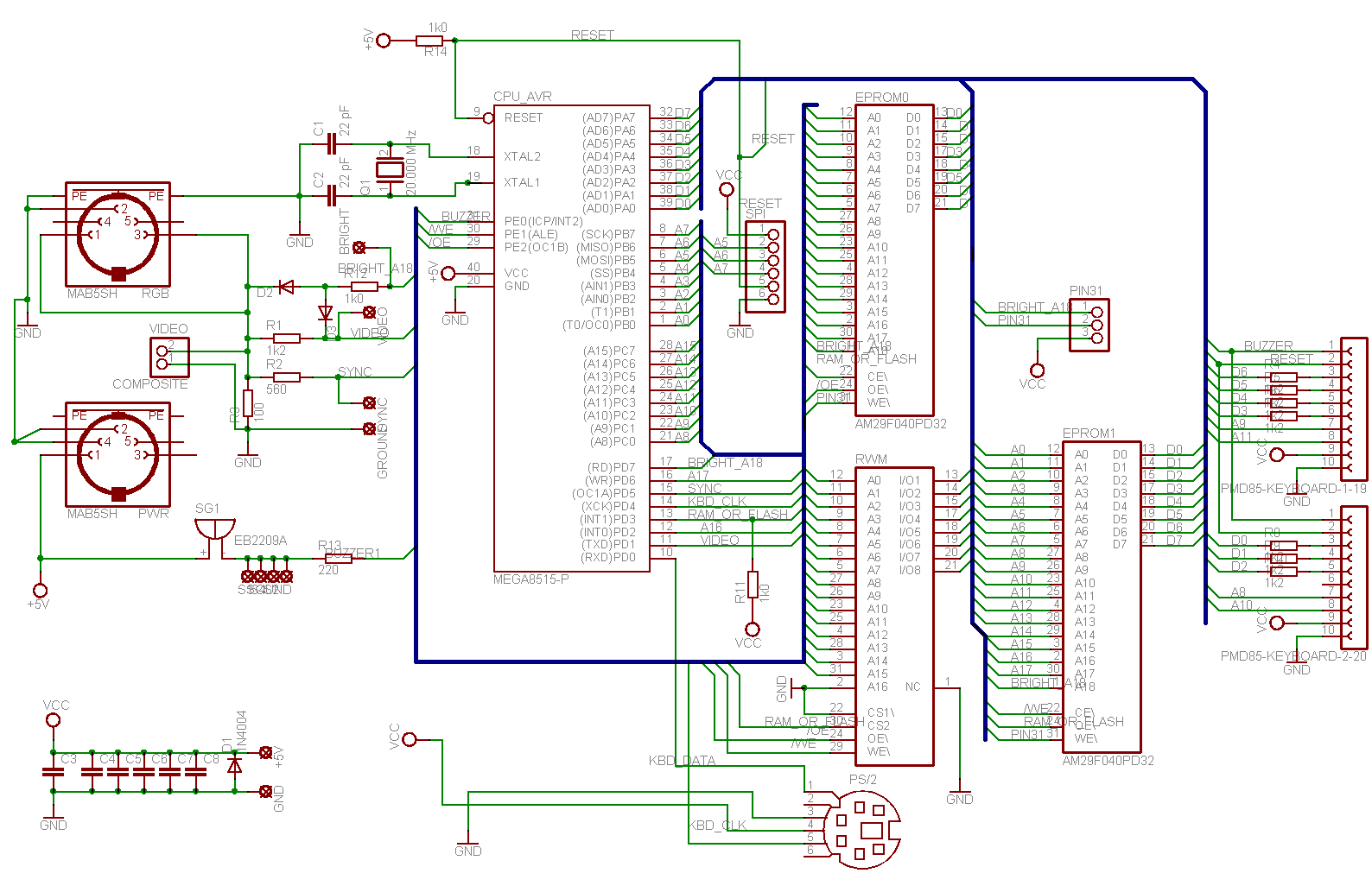

Výzva... ale keď dáte fulltime, výsledky sa dostavili. Koncom júla 2023 funguje verzia ktorá snúbi 8bitového veterána ATMEGA8515-16, taktovanú na 18.432 MHz s farebným 3 bitovým RGB výstupom na SCART. Onboard je aj MIF85, obvod Philips SAA 1099.

Pár poznámok:

zapojenie len 5 integrovaných obvodov...

procesor ATMEGA8515-16PU (všimnite substring 85, to nie je náhoda)

Ram 128KB IS61C1024

register 74373 (expandér IO)

Eprom 27080 alebo 27801. Možnosť osadiť obe EPROM. Pracuje sa aj na verzii s 27C160.

zvuk SAA 1099

SCART DIN7 - TV výstup RGB + je vyvedený aj stereo zvuk z MIF85. Kábel som použil segaMegaDrive2. Čistá práca.

PS/2 Konektor - pripojenie PS/2 myši, alebo PS/2 klávensice

Power connector - DIN5 - napájanie +5V, GND

PMD85 FRB20 konektor na zabudovanie do pôvodnej krabice PMD85

Joystick interface

Emuluje sa PMD85-1 a PMD85-2A, vrátane ALLRAM režimu.

Na taktovanie MIF85 je použitý 8 MHz oscilátor... Dlho som nad tým premýšľaľ, ako sa mu vyhnúť... napr 24/3=8... alebo dynamicky prepočítavať frekvencie a taktovať napr. 9 Mhz. Ale manuál nepustí. MIF85 samozrejme funguje s prerušeniami od časovača, a po resete sa softvérovo vynulujú registre, aby nepískal posledný tón donekonečna.

ColorAce - áno funguje krásne. Nie je úplne ideálne, pár MHz procesorového výkonu by som potreboval ešte. Zobrazovanie ide krásne, 36 KB videoram, 3bity na pixel, všetko atmel zvláda. Problém je pri zápise do videoram, rutina má 140 bajtov = 140 clocks. Zmiešavanie farieb z dvoch bajtov nad sebou, robím "poctivo"... Na zápis 1 bajtu do videoram sa 2 bajty načítajú a zapíše sa 6 bajtov. Každý pixel má 4bity, z toho 3 sú RGB zložky. Výkon pri bežných hrách je dostatočný, možno pri listingu DUMP 1234 trošku vidieť oneskorenie voči originálu PMD85, nič vážne.

režim RGBW by samozrejme problém s výkonom vyriešil. Ale zase 4 vs 8 farieb... no neviem... Ak to nepojde podobrotky, potajme som v Eagle nakreslil verziu s dvoma ATMEGA8515. Jeden ako grafický koprocesor pre RGB.

BITSOUND - momentálne nefunguje optimálne, zvuk sa sampluje len každých 64 mikrosekúnd. Tzv. 15625Hz, frekvenčne ohraničuje výstup na tých max 7-8 kHz. Zvažujem zneužiť MIF85 na generovanie bitového zvuku, ako koprocesor k atmelu.

Poznámka:

PMD85 v roku 2023 rozvíjajú tieto dielne:

RM Team

Sindik.at

Libor LA

Zdenek6

Wex

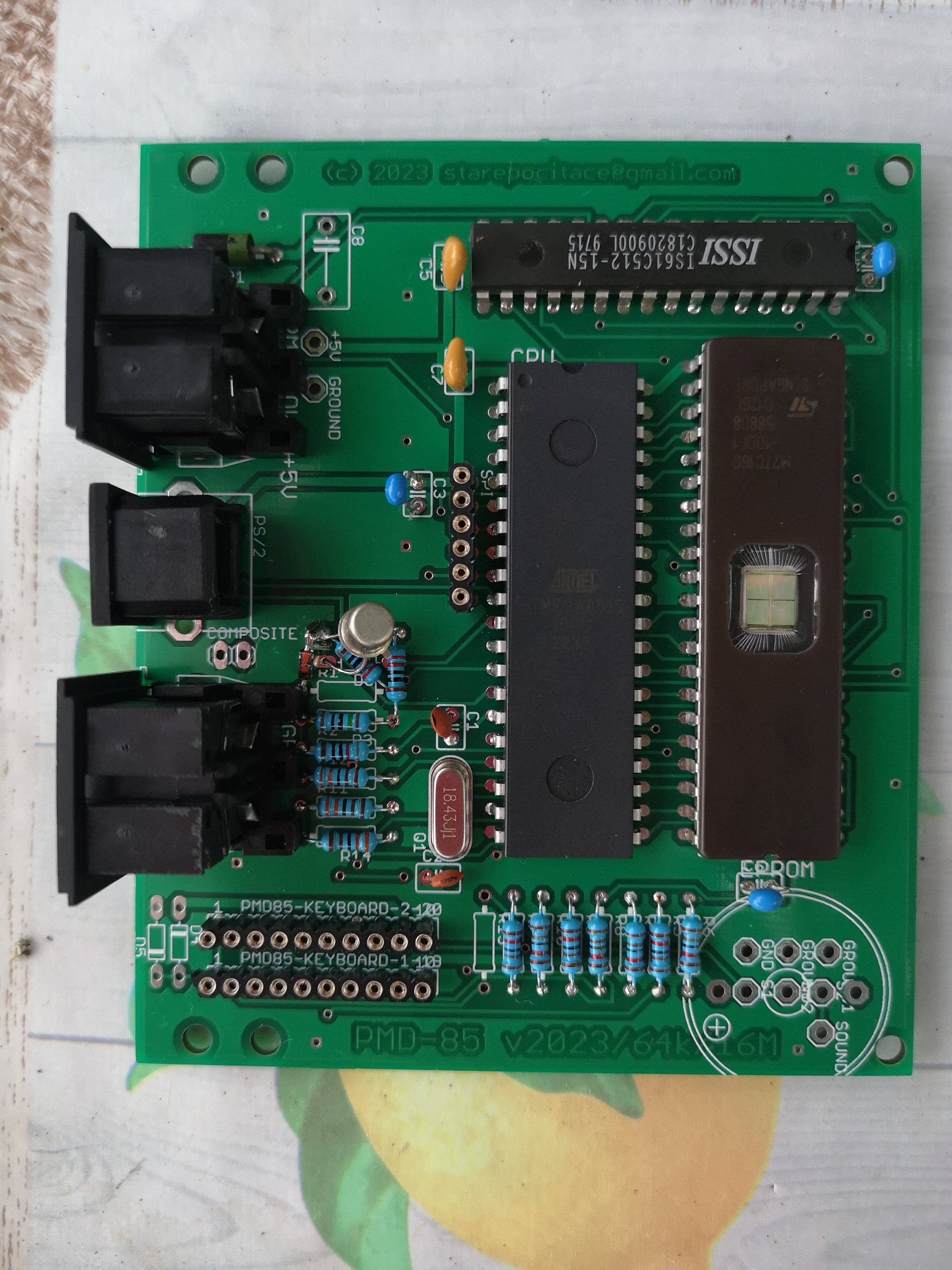

PMD-85 verzia 2023 + 16 Mbit EPROM

V júli 2023, medziobdobí, keď bola hotový PCB už MIF85 verzie, sa mi zacnelo, miniatúrna, ešte monochrom, krásna trojintegráčová verzia PMD85 so 16 Mbit EPROM 27C160. Na tejto verzii som aj odladil Mouse602. Na 35 GPIO a 8bitový Atmel slušný výkon. Kryštál 18.432 MHz. Ako vidieť mixér na ČB sa na poslednú chvíľu invertor s tranzistorom spáchal. BITSOUND samplovaný každých 8 mikrosekúnd, tj. 125 kHz.

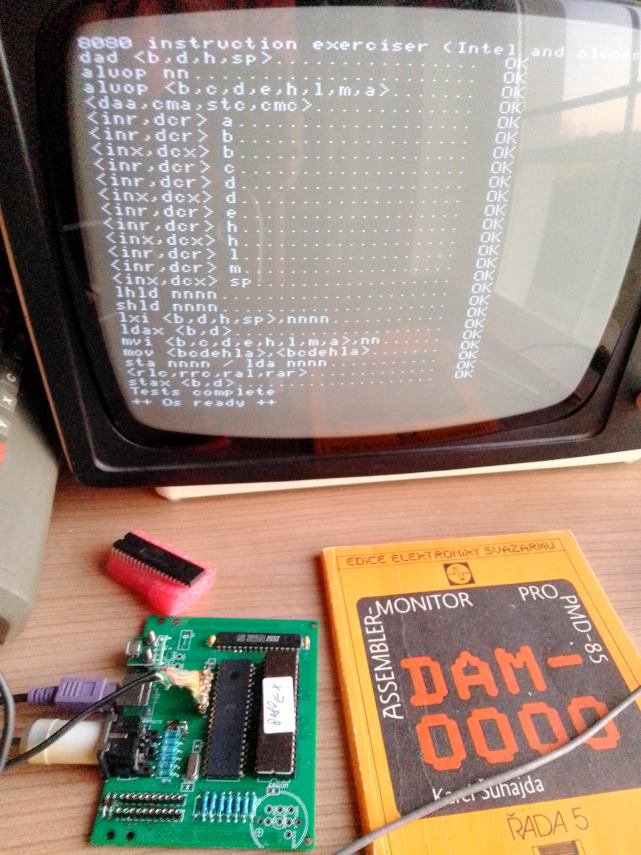

V novembri 2023 sa mi podarilo, po byteFeste doladiť úplnú binárnu kompatibilitu s originálnym INTEL 8080. Problém bol v hraničných situáciach pri inštrukcií DAA a pri nastavovaní AC bitu pri ANA operáciach. Podobne nastavovanie AC bitu pri dekrementácií DCR. Tu mi pomohlo ako to v 8080 asi funguje. Obsahuje totiž len jednu 8bitovú úplnú sčítačku. Pri odčítaní (SUB alebo SBB) sa druhý operand invertuje, CARRY-IN sa invertuje (tj. CIN=1 pri SUB a CIN=not CY pri SBB). Potom prebehne len 8bitové sčítanie. AC bit sa zoberie prenos C3, a CY sa zoberie negácia CarryOUT=C7 zo 7.bitu. Podobne dekremenácia je pripočítanie registra a hodnoty -1, tj. 0FFh. Vtedy sa AC bit nastaví zadarmo sám správne. Pri inštrukciách AND sa AC bit nastavuje podivne, ako logický súčet tretích bitov operandov. Takže exerciser aj na implementácií na architektúre ATMEL AVR už ide bez akejkoľvek odchýlky.

Pri inčtrukcií DAA ale Exerciser 8080/85 mi hlásil CRC error. Exerciser testuje zjavne na všetkých kombináciach AC+CY+A. A zistil som, že nie je úplne presný výklad inštrukcie DAA v originálnom 8080 Programmers Manual.

Konkrétne v bode 2, ked sa rozhoduje kedy má pripočítať hodnotu 60h. Nestačí len podmienka CY=1 alebo horný nibble (po prípadnom pripočítani 6) má hodnotu vyššiu ako 9...

Napríklad keď je situácia AC=C=0 a A=FFh. Síce neviem ako pri BCD aritmetike dôjdeme do takého sympatického stavu, avšak inštrukcia DAA môže byť vykonaná kedykoľvek, pri ľubovoľnom stave procesora, on sa ho nezľakne. Dokonca aj po inštrukcií ktorá nenastavuje AC flag.

Tu podľa bodu 1 sa pripocita 6. Ale už nepripočíta 60h (medzivýsledok je totiž 05h, horný nibble je 0). Mne zafungovalo to, ze v bode 2 testujem hodnotu A este pred pripocitanim 6, a porovnavam s hodnotou 99h. V pripade AC=C=0 a A=FFh po DAA ocakavam v A=65 a to asi aj správna hodnota na fyzickom 8080, ktorú aj Exerciser80/85 očakáva.

Tiež si myslím, že 8080 určite interne nerobí 2 sekvenčné korekcie pri DAA, ale len jeden súčet s hodnotami 0, 6 alebo 66h, ktoré získa z jednoduchej kombinačnej logiky. Viac času tam ani nemá, keďže DAA trvá 4T, čo ju radí k najrýchlejším operáciam, trvá kratšie o 1T ako MOV r,r. Takže určite sa tam procesor veľa nelopotí.

_daa: ; corrected version i8080 on AVR, 17 steps

clr tmp_reg2 ; correction

mov ZL,A

andi ZL,0x0f ; low nibble of A

cpi ZL,9 + 1 ; nibble is > 9, ... 10,11,12,13,14,15

sbrs PSW,ATMEL_H ; or AC=1

brlo noadd6

ori tmp_reg2,0x06

noadd6:

bst PSW,ATMEL_C ; load old CY into T bit

cpi A, 0x99+1 ; high nibble of A

sbrs PSW,ATMEL_C ; old CY

brlo noadd60 ; below A0... 00 az 9F

ori tmp_reg2, 0x60

set

noadd60:

add A, tmp_reg2 ; also AC is set, CY is set manually via T bit

out last_result,A ; for calculate Parity bit

in PSW, SREG ; load new SZ, later we copy new CY(bit T) and new AC ( tmp_reg2)

bld PSW,ATMEL_C

Magická inštrukcia DAA sa používa napríklad aj pri konverzií 4bitové čísla na hexa ASCII reprezentáciu. To klobúk dolu, kto toto vymyslel:

PREVOD1: ; prevod monitor PMD85/2

ANI 0FH

CPI 10

SBB 2FH

DAA

PREVOD2:

ADI 90H

DAA

ACI 40H

DAA

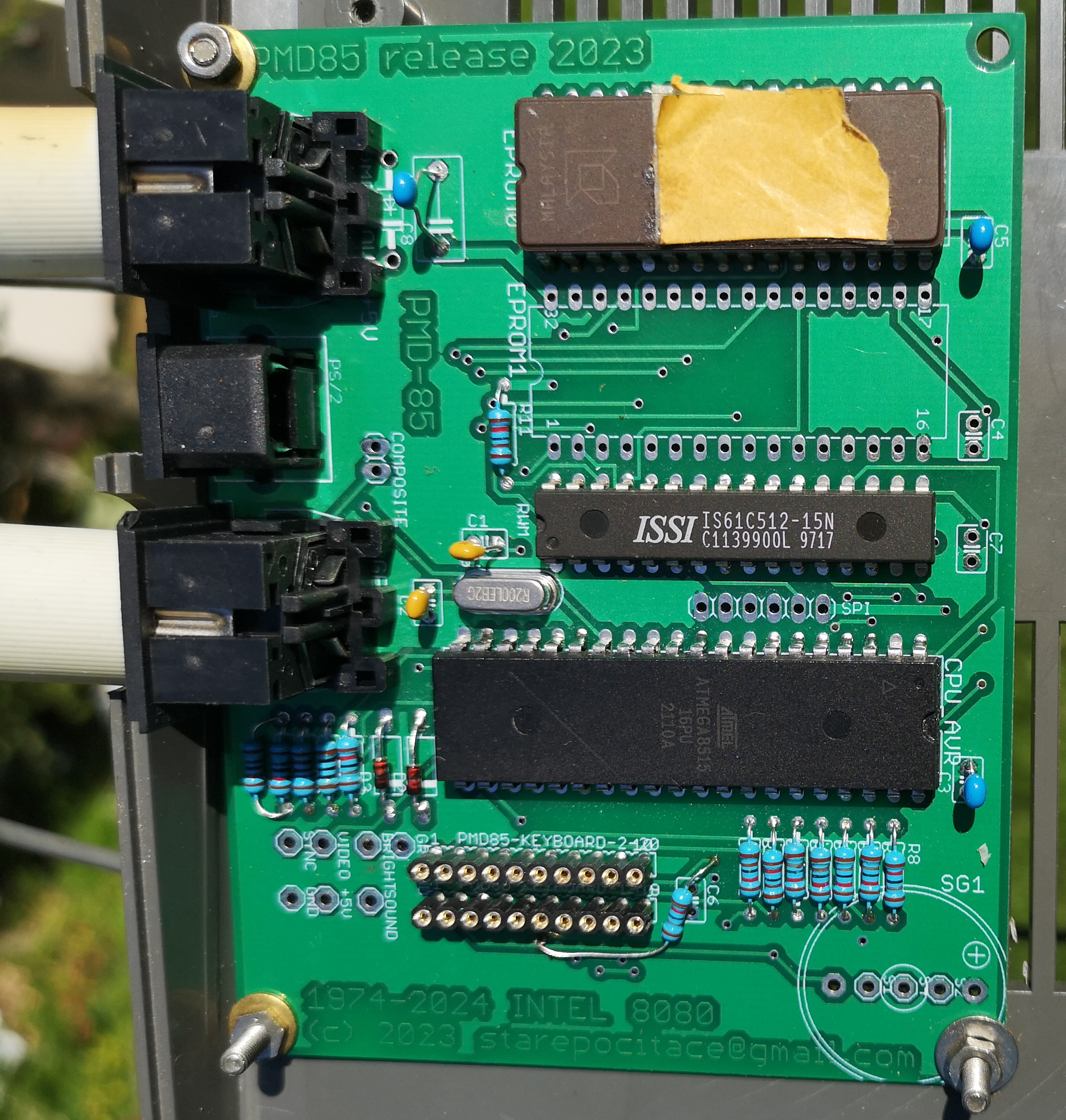

PMD-85 verzia 2023

Rukavica bola hodená; rukavicu som zodvihol. A tak vznikol ďaľší hardvérový emulátor/simulátor/opravná sada/klon PMD-85 verzia 2023. Čiže je to vlastne nový mainboard pre PMD-85, vhodný na zabudovanie do pôvodného PMD85. Je to voľné pokračovanie Urob si sám PMD-85, ktoré beží na ATmega128. Určite nie som sám, ktorý snívame o novšom mainboarde pre PMD85. Nápad dobovej repliky-klonu však kazí istou odlišnosťou napr. 8085 (chýba paritný bit, iné časovanie), Z80 (zložitejšie pripojenie, tiež Parity/overflow bit). A procesor 8080 sa samozrejme nevyrába dnes, ale dá sa kúpiť, za rádovo 3-10 eur. Ale vyžaduje 3 napájacie úrovne (-5V, +12V, +5V) a minimálne 2 podporné IO. Ako som na vlastnej koži zistil, tak aj také hradlo MH7400 stojí 0.40-0.60 eur. Pri PMD85, obsahuje odhadom 25 TTL IO. No ak počítam čistú repliku PMD85, treba si pripravit aspoň 100 eur.

Ciele projektu:

* plne 8 bitový design

* DIL design

* napájanie +5 V

* doska plošného spoja 10 cmx10 cm (obmedzenie freeware Eagle)

* doska má mechanické rozmery a konektory napájania a RGB ako pôvodne PMD-85

* PS/2 konektor na pripojenie externej klávesnice (ala keyFace) + PS/2 mouse602

* 18.432 MHz XTAL ako pôvodné PMD-85

* 20 pin FRB konektor na klávesnicu pôvodného PMD85

* 2 MB EPROM 27C160 (mám aj verzie 27C080, 2x27C040).

* kvalitný zvukový výstup, schopný prehrať high-freq BITSOUND

* čo najmenej integrovaných obvodov

* ja som subjektívne zaťažený na PMD-85-1, takže monochrom + atribút blikania + atribút zvýšeného jasu (pardon, originál má byť 50% jas).

* AllRAM režim

* integrované MIF85.

Čo sa podarilo?

Mainboard je postavený na ATMEL (pardon, už Microchip) ATmega8515 taktovaný na 18.432 MHz. Verzia DIL40, má až 35 IO bitov/portov. Má skvelých 8KB FLASH, čo je naoko málo, ale stačí. Je však nádej, že Microchip časom vyrobí chip s veľkou FLASH aj SRAM. Momentálne skúmam aj nový AVR128DA28, ktorý má DIL28 púzdro a 128 KB FLASH a 16 KB SRAM a beží na 24 MHz.

Tých 20 MHz jednak poskytuje krajší obraz, kvôli tomu, že generujem lepší aspect ratio X:Y ako pôvodné PMD-85, kružnica konečne nevyzerá ako vajce či elipsa apod. Nie je problém ani s 18.432 MHz, vtedy je to ako originál. Ale 20 MHz umožňuje generovať zvuk v kvalite Libor L.A. BITSOUND. Napríklad nová hra Arkanoid. Pôvodné riešenie generovalo zvuk s maximálnou frekvenciou 7.8 kHz, keď tam Libor posielal frekvencie vyššie, už to viach chrčalo, ako lahodne hralo. Teraz som dokázal popri generovaní video výstupu v rýchlosti 6 Mbps, generovať aj zvuk o maximálnej frekvenci 62.5 kHz. Áno, ide to, v podstate počítam takty I8080, spomalené primerane o pôvodný videoprocesor a vzorkujem každých 8 µs. Vlastne 48 µs kreslím TV riadok, a v ďaľších voľných 16 µs simulujem beh procesora 8080, kde každých 2 µs vzorkujem sound port. Následne v ďaľších 64 µs odvysielam zvuk, spolu s obrazom.

Klávesnica PMD-85 je pripojená cez DIL 20 precíznu päticu, namiesto FRB konektora. Pätica by ideálne mala byť 90° ohnutá, ale stačí aj priama, káblik od pôvodnej PMD85 klávesnice sa tam v pohode zmestí.Stĺpec klávesnice sa scanuje každých 256µs, tj. každý 4 TV riadok. Celá klávesnica za 4096 µs. Vytrápil som sa tiež s tým, keďže je to pripojené len cez odpory na zbernicu, ala ZX Spectrum. Klávesnica samozrejme môže byť odpojená a pripojená externá PS/2. obe odpojená aj obe zapojené. Takže zvláda aj dvojhru Tankovej bitky. Pripojený je reproduktor, žltá LED, červená LED svieti len pri RESETE, kvôli nedostatku IO pinov.

Špeciálne funguje SHIFT+RESET+STOP, slúži na RESET a cyklické prepínanie verzií PMD-85-1, PMD-85/2A BASIC-G a PMD-85/2A MONITOR. Tj. držanie klávesy STOP počas RESET spôsobí prepnutie verzie PMD-85. Na PS/2 klávesnici sa prepína ALT+1, ALT+2, ALT+3 tieto tri verzie. ALT+S zobrazí screen s InfoScreenom. Samozrejme funguje aj BASIC G/1.0.

RAMka je ako inak statická 64 KB, úzka DIL32 ISSI IS61C512-15N (prípadne kompatibilné napr. UMC UM61512AK). Je to super ramka, rýchla ako raketa 15 ns (!), kedysi sa používala ako CACHE pre 386 a dá sa aj v roku 2023 kúpiť. Tak či onak, skrz buffrovanie vstupov/výstupov Mega8515 treba čakať 2 takty od vyslania adresy po načítanie dát. Čiže občas musím čakať s NOP. Kvôli nedostatku IO pinov, je odpor R11 pullup na pine PD3 a trvalo vyberá RAM, keď je pid PD3 prepnutý na vstup. Počas serializácie TV riadka sa rotáciou dát niči celý obsah portu PORTD, bit7 je jasová zložka BRIGHT, a bit1 je VIDEO.

FLASH/EPROM sú dve AMD 27C040 alebo takmer nezohnateľné AMD 29F040B. Čiže 2 * 512 KB = 1024 KB. Prepínač Eprom FLASH rieši rôznu funkciu pinu 31. U Flasky je to /WE a u EPROM je to A18. Pin číslo 1 je trvalo pripojený na A18, u EPROM je to V_PROG programovacie napätie, ale v bežnom režime je don't care.

Prepínanie RAM a ROMiek prebieha inak ako v predošlých verziach HW emulátora. RAMka je defaultne prepnutá na kontinuálne čítanie, aj počas práce videoprocesora. Ak sa má robiť zápis, checkuje sa 16bitový časovač TCNT1, či nepríde k prerušeniu od videoprocesora počas zápisu. Podobne čítanie z ROM, akurát si rezervujem viac času na operáciu. Aby sa zabránilo prestojom a blokovaniu zápisu do RAM videoprocesorom, niekedy sú 8080 inštrukcie načítané z RAM skorej ako je urobený zápis výsledku predošlej inštrukcie. A niekedy v normálnom poradí. Viď rutina writeMemoryExecute.

Magnetofón funguje aj vo verzií PMD-85-1, aj PMD-85-2A. Samozrejme ako rýchlik. Funguje aj časovanie cez UART, ala Hlípa, Arkanoid, Flappy2K.

Napájanie je kompatibilné so zdrojom PMD-10, cez male-male DIN5 adaptér, napr. mgf kábel. DIN5 male PCB 90 angle connector nezohnateľný.

Myš PS/2 ala Myš 602. Ide super; zatiaľ viem o Mínach a o FunnyFruits +gredit. Emulácia PS/2 myši ako mouse602 ide super. Už som si objednal z bazoša ďaľšie PS2 myši. Začal som s Mínami od Libora LA, a doladil som aj pre FunnyFruits myš. Tam len ide o to že ako rýchlo súkať dáta na port 8C. Mínam stačilo 1 read a pri ďaľšom reade už mohol snímač vykázať inkrementáciu. Pri funnyFruits hodnotu na porte podržím 3 čítania a ide super. Samozrejme že sa žiadne zmeny polohy nestrácajú... Implementačne je inkrementácia/dekrementácia gray kódu cez paritu, xor, rotácie. Takže míny na PMD85 s optickou myšou ... Bol to impulz, tieto nové programy a budem rád keď sa aj SOLITéR od Romana Bórika dočká upgradu ;) Myš funguje v pool režime, bez prerušení, tie sa neemulujú, ani PIT 8253, ani jeho prepojenia na systémovom konektore. Prerušenia na 8080 je iné kafé, ale u Atmela také čáry-máry...

EPROM 27C160 áno, poradilo sa. 16MBit. To je 2048krát viac ako pôvodná eprom 2708. +5V TTL úrovne. Je to najväčšia 5V 8bitová EPROM pamäť. Dokonca sa podarilo bez chyby na plošáku, keďže najskôr som kúpil pamäte až potom kreslil plošák. EPROM má púzdro DIL 42. zapojená v 8bitovom režime. Programovanie bol trošku experiment. Ale willem na LPT pomohol. Tam sa takmer všetok SW zmestil, čo sa zachovalo na PMD85. Čiže PMD85 tvorí svätá trojica IO 8080+8228+8224 a v klone PMD85 máme ATMEGA8515+61C512+27C160. Krása.

ColorAce práce pokračujú. Boli indície že multicolor verziu nemá šancu 8bitový Atmel utiahnúť.... ale má... opäť je srdcom ATMEGA8515-16, taktovaná na 18.432 MHz a vyššie. Hadrvérovo sa líši od monochromu. Je tam samozrejme potrebná zmena plošáku a softvéru. Namiesto 1 bitu RGB verzia posiela 3 bity. Inštrukciou ASR+OUT som dokázal vyslať naraz 2 bity (jasový atribút a video). Teraz potrebujem vyslať naraz 3 bity každé 3 takty (každých 3x52 ns=162 nanosekúnd). Túto treba vzdať hold prvolezcom (Ing Roman Kišš) a aj súputníkom (Dušky, rombor, Libor LA), ktorí v tejto nanosekundovej oblasti boli úspešní. Alebo tí, čo napália rovnice PMDčka do hradlového poľa a bude fungovať... A hlavne ich odladia... Inštrukciou ASR, LSR apod neurobím rotáciu naraz o 3 bity. Preto som vymyslel zapojenie 128 KB SRAM IS61C1024 (sestra IS61C512). Proste hrubá sila. Dušky si taktiež pomohol, navyše DRAMkami... Je to vymyslené tak, že PORTE, ktorý ma 3bity, sú bity RGB, pripojené cez odporový delič rovno na SCART RGB konektor. Pamäť IS61C1024 je rozdelená na 64 KB - klasika, adresný priestor 8080. A tá druhá 64 KB je videoram. True color to nie je. Na 288*256 by som potreboval 72 KB videoram. Pri 256 farbách, 8bpp. Keď sa uskromním so 16farbami, vystačí aj 36KB. A bingo! Použijem 4bity na pixel, z toho 3 bity sú RGB a 1bit je vata/alignment. No dobre, ale ako odrotujem register o 3 alebo 4 bity? hhhh, máme SWAP inštrukciu, rotácia o 4 bity doprava/doľava... To je naša rotácia. Dnes zobrazovanie už mám rozchodené, to ide 36KB * 50 Hz = 1800 KB/s, tj. 10,8 Mbps. Pri tomto riešení sa ťažisko presúva do zápisu do RGB videoram. Tam z jedného bajtu, čo je 6 pixelov, budem musieť do RGB videoram zapísať 3 bajty. Čo je horšie, realisticky budem musieť zapísať 6 bajtov, aj do mikroriadku nad/pod, ktorý zdieľa farbové atribúty.

No 14 rokov som odolával ColorAce, ... Máme tu však novú dobu, komunita vyvinula softvér, ktorý používa ColorAce ;) Deti už mám väčšie... Koronu som prežil... Ešte sa treba pohrať... Kríza stredného veku. Na PMD85 ide denne 8 hodín.

Prinajhošom hrozí že ColorAce bude pomalšia verzia (tj. vo výsledku pôjdeme do vyššej frekvencie CPU)...

Čo sa zatiaľ nepodarilo

* Vyladiť mixér composite video, hodnoty odporov.

* Vyvedenie zbernice na interný aplikačný konektor. Aby sa dalo pôvodné periférie PMD pripojiť.

* kopec detailov vernejšie emulovať :D :D :D

Na čom sa to momentálne zaseklo?

15. mája som zistil že mám problém s interným oscilátorom pri vyšších frekvenciách ako 18.432 MHz, pri výrobe ďaľších kusov PMD85 v2023. Mám kúpených zopár ATMEGA8515-16PU, ale nechcú ísť stabilne na aspoň 20 MHz. Áno, overclocknuté o 25%. Tie novšie mám kúpene s datecodom 2110, aj originál farnell 2235, čiže úplne nové z linky. Najviac frustrujúce je to, že prapôvodný 20 ročný ATMEGA8515-16PI s kódom 0313, čiže z roku 2003 ide aj na 24 MHz. To je overclock o 50%, a ide ako víno. Nehovoriac že išiel v zapojení aj po 20 rokoch (tj. nezistil som data retention problém, FLASH). Preto som nikdy neriešil toto ako problém. Proste tá prvovýroba bola kvalitnejšia, bezproblémová. Skúšam aj externý oscilátor (CKOPT=0, CKSEL0-3=0) a opäť ide stabilne len ten čip z roku 2003. Riešenia sú viaceré:

* taktovať len do 18.432 MHz (tam je problém len s chraplavejším zvukom)

* urobiť výskum oscilátora, fuses CKSEL0-CKSEL3, nájsť vhodné kombinácie kapacít a kryštálu na stabilný beh.

* zohnať lepšie čipy MEGA8515, staršie. Tie s bielou potlačou a pin1 označený trojuholníkom.

* použiť obdobný čip čo podporuje 20MHz natívne, napr ATMEGA644 DIL40, ATMEGA1284 DIL40, z novších MEGA4908 alebo AVR128DA DIL28..... To však znamená prekresliť plošák, a pravdepodobne použiť ďaľší pomocný register. Tie novšie majú totiž ADC na sebe, a to je minimálne o 2 piny menej voľných. * priamy nástupca ATMEGA8515 v prevedení DIL40 je ATMEGA162... porty, púzdro totožné, len SRAM a FLASH dvojnásobná. Má pekných 35 GPIO, organizovaných 4*8+3. Plus navyše periférie ako 3xPWM. Tu treba povedať že ATMEL vyrába/vyrábal rádovo stovky modelov procesorov AVR.

Čo tak použiť ESP32 Lolin S3, Raspberry-pi pico, STM board?... No ešte to s AVR skúsme :D Zase kedy som si vyskúšal za chodu procesora a aplikácie vybrať/vymeniť kryštál a program išiel bez vady ďalej.... Objednal som ATmega162, čo nie je žiadny výkrik techniky v roku 2023, ale má DIL40 púzdro a 35 GPIO.

16 may

Úprava loadovania programov - počas nahrávania programov do PMD85, ak stlačíte SHIFT, dôjte k načítavaniu hlavičiek len, tj. preskakuje telá súborov.

20 máj

Stále ma láka pôvodná veľkosť kryštálu 18.432 MHz. Výkon je postačujúci, ale pri počítaní taktov a presnom časovaní (samplovaní) zvuku je ho stále málo. Doteraz sa PMDčko emulovalo len 16 us z každých 64 us (TV riadok). Spravil sa veľký pokrok, že aj 55 nezobrazovaných TV riadkoch, ktoré využívam plne na emuláciu. Zvuk sa plní do buffra 2048 bitov, a odosiela každých 8 us. časovač TCNT0 generuje prerušenie každých 8us. To je teda aždých 147 taktov AVR, resp. každých 16 taktov 8080. Nedostatok výkonu sa čiastočne vyriešil, ale stále bolo počuť že občas jitter - chrapot, keď nestíha AVR a buffer je prázdny. Napr. v hre AUTO, sa čakacia slučka je z inštrukcií LHLD a SHLD. Zápis v AVR podstatne pomalší ako čítanie, musím vždy zistiť či zápis stihnem, potom prepnúť zbernicu, vykonať zápis. Sekvencia/ signálov na zápis je postatne zložitejšia.

23 máj

Hardvérový stack implementovaný. ide ako delo. Delo ako delo. Ide len o zrýchlenie emulácie, keď súvisiace PUSH a POP ( resp. CALL a RET) sa vykonajú bez reálneho zápisu do RAM pamäti, do zásobnika. Kľudne si môžete SP nastaviť aj do pamäte ROM, aj tak inštrukcie PUSH+POP budú fungovať ako predpokladáte. Na slušné používanie to funguje slušne a rýchlo. Ale samozrejme má to prekonateľné muchy. Napr. samospúšťacie programy, ktoré prepíšu stack apod. Ten koncept PUSH/POP a CALL/RET prípadne XTHL fungujú elegantne. Horšie prípady nastávajú keď sa zásobník zneužíva, napr. sa z neho číta viacej ako sa zapíše, alebo na zápis do videoram. Ďaľšia možnosť je, zápis viacej dát do zásobnika, ako je v ATMELi na to určený buffer, momentálne 160 bajtov. Citeľné zrýchlenie je už aj pri pár bajtovom buffri, najväčšia prevádzka je vždy na vrchole zásobníka.

Konkrétne napr. hra KURA, používa elegantný scroll obrazovky takto:

XTHL

DCX SP

DCX SP

XTHL

DCX SP

DCX SP

XTHL

DCX SP

DCX SP

XTHL

DCX SP

DCX SP

XTHL

DCX SP

DCX SP

Tento kúsok kódu preniesol 10 bajtov vo videoram o 2 bajty doľava. Tento funguje vďaka tomu že pri akejkoľvek nútenej zmene SP registra zapíšem hardvérový stack do reálnej RAM. Tuto konktétne treba poznamenať že inštrukcia DCX SP a INX SP narúša integritu stacku, že posúva SP len o jedna, namiesto o dva bajty.

Scroll 10 bajtov doprava, bol implementovaný takto:

XTHL

POP PSW

XTHL

POP PSW

XTHL

POP PSW

XTHL

POP PSW

XTHL

POP PSW

tento kúsok kódu sprvoti nechcel ísť, a Kuriatko išlo len na ľavej časti obrazovky, lebo pravá ostávala vždy len prázdna. Z hľadisla emulácie ide o dve najdlhšie trvajúce inštrukcie, aj z hľadiska toho že PSW musím pracne vypočítať, aj paritný bit, ktorý u ATMEL chýba.

Trošku som sa vytrápil aj s hrou BLUDISKO, tam začala zase hudba chrčať. Tam bolo v časovacej slučke zvuku použité 6*XHTL

XTHL

XTHL

XTHL

XTHL

XTHL

XTHL

Mal som však len chybu, že po vykonaní XTHL sa takty len spočítavali a netestovalo sa 8 us.

Taktiež som opravil časovanie inštrukcií, počítam takty, spomaľovanie podľa videoprocesora, podľa článku Takty i8080 v PMD85. Pre istotu som tu tabuľku s predĺžením taktov aj uložil k sebe. Snáď mi Zdeněk autorské práva prepáči, bola to práca prepočítať a celé to spísať.

Čo sa týka zásobniku, tak emulátor čo spustí kód BASICu sa dá považovať za dokonale správny :D Sú tam zásobnikové skvosty, napočítal som 52 x XTHL a 3x INX SP. A tá posledná inštrukcia INX SP, o ktroej som si myslel že sa používa v páre, tak v BASICu:

PUSH PSW

INX SP

PUSH B

PUSH B

XTHL

POP B

jún 2023

Vrátil som sa k pôvodnému riešeniu keď pri zápise do RAM sa nepoužíva TCNT1. Celkovo to vychádza rýchlejší a kratší kód. Zápis do pamäte RAM je časovo najnáročnejšia operácia, kvôli synchronizácií s videoprocesorom.

* oprava jasového atribútu. Tu som zistil že nie je také ľahké urobiť dokonalý mixér na generovanie composite video (len z diód a odporov). Jasový atribút má význam 50% jasu a preto skúmam spraviť tranzistorový invertor. Komplikácia je samozrejme, že čierna s 50% jasom má byť stále tá istá čierna. Aj tranzistory KSY71 majú oneskorenie rádovo 20 ns, čo je cca 1/2 inštrukcie atmelu a na TV je to vidieť, že obraz nie je dokonale ostrý. Hodnoty odporov R1 = 1 - 1.2 kOhm, R2=560 Ohm, R3 = 100 Ohmov, sú empirické. Testujem aj mixér s dokonalými a vedeckými hodnotami R1 = 390 Ohm, R2= 220 Ohm, R3 = 180 Ohmov, ktoré by mali generovať správnu amplitúdu bielej, čiernej aj sync úrovne pri záťaži 75 Ohm.

* optimalizácia generovania paritného bitu. Áno oproti klasike (rotácie, swap, xor), ušetril som 1 inštrukciu (9%). Prinajhoršom by sa dala pripojiť 74180 ako koprocesor. Tu treba povedať, že mnohí sme zastali, v klonoch sa nedajú priamo použiť procesory 8085 ani Z80. Procesor 8085 nemá paritný bit, takže PMD85 BASIC-G nespustí. No neviem, netradičné použitie paritného bitu na testovanie typu premennej. Rovnako Z80 okrem iného časovania inštrukcií, má inak nastavovanie flag-ov.

* skúmanie ako naprogramovať pamäť 27C160, ktorá je síce DIL42, 16bitová eprom, ale je dostupná a má 8bitový režim čítania, a 16 Mbit = 2 MB kapacitu. ELNEC odporúča na hobby použitie WILLEM Programmer, absolútna klasika na LPT port !!!. Tak čakám čo príde z aliexpressu. Plus adaptér 16 bitové epromky

* keď som si spustil pôvodné PMD85 a implementáciu v ATMega8515, nie som si istý, či taktovanie je identické, preto som posunul časovanie inštrukcie POP z 12 na 10 taktov. Testujem na PMD-85/2A, príkaz DUMP 0000... Alebo bude opäť dakde neodhalená nedokonalosť alebo preklep.

júl 2023

* implementácia myši602, fyzicky pripojená je akákoľvek PS2 myš - optická, guličková. Zopár bajtov kódu ;)

* Eprom 16MBit 27C160 !!!

* doladiť - ROM0 - demko v BASIC-G

* 0x30 narodeniny Ikon

* doladený BASIC-2A. ALLRAM režim, menší problém. doladené.

september 2023

Optimalizácia - zapnutím bootloaderu na adresu 0xC00 a presunutím RESETu a obsluhy prerušení od časovačov som získal to, že register ZH=0. Register ZH je trvalo nula a adresuje mi aj rozskokovú tabuľku 256 inštrukcií cez pamäť programu IJMP a rovnako adresujem zmenou ZL, aj nultú stránku internej SRAM 0x60 - 0xFF. Tým sa mi aj uvoľnil jeden register a zároveň zrýchlil a skrátil kód, keďže nemusím načítavať vyššiu časť adresy, tá je stále 0. V SRAM pri ZH=0 sídlia všetky premenné, tabuľky typu rgb_table. Dokonca pekne funguje aj skátené ldd r0,Z+5 . Po 20 rokoch pochopím tento procesor m8515, že register Z adresuješ adresy 0x60-0xff, registrom Y 0x100-0x1FF a registrom X adresy 0x200-0x25F. Procesom mega162 má SRAM pamät zarovnanú od 0x100, ... má zase až 1 KB.

** pálim EPROMky 27C801 ** 8 Mbit = 1 MegaByte.

** Implementácia ROMMegaModulu ** Kôli spusteniu Bad Apple demu a hry Šach. Tu som si to vyžral do dna. A otravoval autora dema Libora LA. Tu som si to oddebugoval a zistil som že po odoslaní CW na 8255 nenulujem vyslanú hodnotu na PORTB, PORTC.

stalo sa toto:

1. monitor PMD85-2/2A na konci TRANFER rutiny nastavi port FAh na hodnotu FF - akoze odpoji PC7=1 ... +12V na epromkach.

2. spusti sa demo BA2 od 0000

3. inicializuje port FB na hodnotu 90. ... orientacia portov ROMPACKu. tu by som podotkol ze emulovana 8255 nenuluje hodnotu portov pri zapise CW (moja chyba)

4. nasledne DEMO bezi... a tam na adresach 1930h pri RST 1 cita z ROM modulu tak ze vysle na port F9 LSB adresy... a na port FA len ked pretecie.... Cize ak port 0xFA nie je vynulovany, tak je stale v nom hodnota z bodu 1 (FF) a cita z adresy nie 000000h, ale 007F00 resp., z vypnutej epromky :D v pripade pmd85-1 specifikacie :D fix:

pred spustenim dema, musim MVI A,0 + OUT FAh + JMP 0000h... Alebo pri zapise CW vynulovat 8255 porty.

ponaučenie: Naozaj existuje klon 8255, ktory nenuluje porty. Niesom prvý, čo to pokazil. Napri OKI 82C55:

MSM82C55A-5 After a write command is executed to the command register, the internal latch is cleared in PORTA PORTC (only). For instance, 00H is output at the beginning of a write command when the output port is assigned. However, if PORTB is not cleared at this time, PORTB is unstable. In other words, PORTB only outputs ineffective data (unstable value accordingto the device) during the period from after a write command is executed till the first datais written to PORTB.

Keď stavať ROMMegaModul, tak len poctivá stará INTEL-TESLA 8255. Temelín ani lietadlo neriadiť cez 8255.

október 2023

Vidíme sa na Bytefeste v Prahe. Kto chce vidieť čo dokáže 8KB kódu AVR assemblera.

mega8515

Procesorov tohto typu mi prišlo viacej kusov; no žiaden veľmi nechce ísť stabilne na 20 MHz, iba ten z roku 2003. V prospech mega8515 je, že má o 3 bity IO portov viac, tzv. PORTE. Iné 20 MHz procesory v DIL40 púzdre majú len 4*8=32 GPIO, vďaka ADC prevodníku.. Nieje problém prirobiť záchytny register. Problém je najmä ten, že prístup k nemu je pomalší. Atmel trošku pokazil AVR že CBI/SBI trvajú až 2takty, čiže zápis do externého registra trvá minimálne 5 taktov, čo je 5x pomalšie ako prístup k normálnemu portu. Nehovoriac o tom, ako pomaly je nastaviť/nulovať jeden bit v takomto registri. Ďaľší problém je, že potrebujem 3 8bitové porty(24 bitov=16 bit adresa, 8 bit dáta). Na zvyšnom 8-bitovom porte sa vylučuje generovanie VIDEO výstupu (rotácia spôsobuje zápis kadečoho aj do iných bitov), s generovaním SOUND signálu a rovnako s riadením /WR, /OE, /CS pamätí. Čiže sú potrebné aspoň 5 registrov, PORTA (D0-D7), PORTB (A0-A7)- PORTC (A8-A15)), PORTD (VIDEO, jas BRIGHT, KB_CLK, KB_DATA, SYNC, SELECT_RAM_OR_FLASH, časť adresy A16, A17), PORTE (SOUND, /OE, /WE). Inak neviem, už pomôžu len procesory v púzdre TQFP64. Je to taký veterán, ale stále je ** in production **. Má nástupcu, ATmega162...

Treba povedať že ATmega8515 z Číny vyzerá skorej ako neoriginálny čínsky klon, ako ten z FARNELL/MOUSER, ale šlape rovnako, má aj bootloader, aj som nenašiel žiadne léčky.

tajné inštrukcie a porty

Momentálne koncom mája 2023, v rámci zjednodušenia a zrýchlenia, priznávam že interne okrem povinnej základnej sady inštrukcií 8080, som si dorobil dve inštrukcie - kódy 0x08, 0x10. Jedna robí writeStack, akýsi flush zásobníka naspäť do RAMKy a je použitá len raz, pri pri zápise dát z magnetofónu, kvôli autostartu programov (z magnetofónu sa nahrá časť zásobníka). Druhá inštrukcia robí readByte z magnetofónu, podobne ako rutina 0x8B6C. Vrátane nastavenia PSW. Tu ide o to, že modely PMD85-1 a PMD85-2 majú úplne inak riešené čítanie dát z magnetofonu. V podstate pre PMD85 dvojku, port 1E funguje ako pre PMD85-1. Len som pre PMD85-2 potreboval občas takú skratku pre C3 6C 8B nahradiť kompaktnejším 10 C9. No celé to asi prikryjem nejakou perinkou, lebo niektoré programy detekujú jednotlivé verzie PMD85-2 podľa nejakého bajtu v romke, napr. 8B6C: C5 . Momentálne som si rutinku 8B6C napísal ako: 8B6C: C5 10 C1 C9.

Tajne ešte bežím ALLRAM režim non-stop, resp. stále bežím v RAMke, kde je len skopírovaná ROM 4K. To však robí problémy s detekciou ALLRAM, každý autor má svojský štýl ;) A robí skúšobné zápisy na rôzne adresy. Niektoré hry sa totiž neuspokoja s tým, že otestujú ALLRAM, ale testujú aj pripojiť ROM a zápis do ROM. V niektorých hrých napr. HLIPA, Highway Encounter som zmazal kontrolu na ALLRAM. Nieje to elegantné, ale funguje ;) Ale asi ma čaká to doklepať do transparentného stavu.

podivné použitie IO Atmelu

našiel som trojicu portov - EEDR, UBRR, EEARL, ktoré používam ako rýchle úložisko 3 bajtov, ako obyčajné registre. Nič viac, nič menej. Nuž 32 vnútorných registrov je málo...

A ako to vyzerá

a čo je v ATmega8515?

Áno, zatiaľ zdieľam plne funkčný kompilát, listing. Pre predstavu:

AVRASM ver. 1.56 pmd.asm Wed May 24 15:20:59 2023

warning : Register already defined by the .DEF directive

warning : Register already defined by the .DEF directive

warning : Register already defined by the .DEF directive

warning : Register already defined by the .DEF directive

warning : Register already defined by the .DEF directive

warning : Register already defined by the .DEF directive

warning : Register already defined by the .DEF directive

warning : Register already defined by the .DEF directive

warning : Register already defined by the .DEF directive

warning : Register already defined by the .DEF directive

warning : Register already defined by the .DEF directive

warning : Register already defined by the .DEF directive

warning : Register already defined by the .DEF directive

warning : Register already defined by the .DEF directive

warning : Register already defined by the .DEF directive

;

; PMDEmu SMALL - AVR based emulator of Czechoslovak microcomputer PMD-85 originally based on I8080

; Copyright (C) 2023 Peter Chrenko <stare********@gmail.com>, Topolcany, Slovakia

;

; This program is free software; you can redistribute it and/or modify

; it under the terms of the GNU General Public License as published by

; the Free Software Foundation; either version 2 of the License, or

; (at your option) any later version.

;

; This program is distributed in the hope that it will be useful,

; but WITHOUT ANY WARRANTY; without even the implied warranty of

; MERCHANTABILITY or FITNESS FOR A PARTICULAR PURPOSE. See the

; GNU General Public License for more details.

;

; You should have received a copy of the GNU General Public License

; along with this program; if not, write to the Free Software

; Foundation, Inc., 59 Temple Place, Suite 330, Boston, MA 02111-1307 USA

;

; PMD.PHP

.include "m8515def.inc"

;***************************************************************************

;* A P P L I C A T I O N N O T E F O R T H E A V R F A M I L Y

;*

;* Number :AVR000

;* File Name :"m8515def.inc"

;* Title :Register/Bit Definitions for the ATmega8515

;* Date :April 16th, 2002

;* Version :1.00

;* Support telephone :+47 72 88 87 20 (ATMEL Norway)

;* Support fax :+47 72 88 87 18 (ATMEL Norway)

;* Support E-mail :[email protected]

;* Target MCU :ATmega8515

;*

;* DESCRIPTION

;* When including this file in the assembly program file, all I/O register

;* names and I/O register bit names appearing in the data book can be used.

;* In addition, the six registers forming the three data pointers X, Y and

;* Z have been assigned names XL - ZH. Highest RAM address for Internal

;* SRAM is also defined

;*

;* The Register names are represented by their hexadecimal address.

;*

;* The Register Bit names are represented by their bit number (0-7).

;*

;* Please observe the difference in using the bit names with instructions

;* such as "sbr"/"cbr" (set/clear bit in register) and "sbrs"/"sbrc"

;* (skip if bit in register set/cleared). The following example illustrates

;* this:

;*

;* in r16,PORTB ;read PORTB latch

;* sbr r16,(1<<PB6)+(1<<PB5) ;set PB6 and PB5 (use masks, not bit#)

;* out PORTB,r16 ;output to PORTB

;*

;* in r16,TIFR ;read the Timer Interrupt Flag Register

;* sbrc r16,TOV0 ;test the overflow flag (use bit#)

;* rjmp TOV0_is_set ;jump if set

;* ... ;otherwise do something else

;***************************************************************************

;***** Specify Device

.device ATmega8515

;***** I/O Register Definitions

.equ SREG =$3f

.equ SPH =$3e

.equ SPL =$3d

.equ GIMSK =$3b

.equ GICR =$3b

.equ GIFR =$3a

.equ TIMSK =$39

.equ TIFR =$38

.equ SPMCR =$37

.equ EMCUCR =$36

.equ MCUCR =$35

.equ MCUSR =$34 ; For compatibility,

.equ MCUCSR =$34 ; keep both names until further

.equ TCCR0 =$33

.equ TCNT0 =$32

.equ OCR0 =$31

.equ SFIOR =$30

.equ TCCR1A =$2f

.equ TCCR1B =$2e

.equ TCNT1H =$2d

.equ TCNT1L =$2c

.equ OCR1AH =$2b

.equ OCR1AL =$2a

.equ OCR1BH =$29

.equ OCR1BL =$28

.equ ICR1H =$25

.equ ICR1L =$24

.equ WDTCR =$21

.equ UCSRC =$20 ; Note! UCSRC equals UBRRH

.equ UBRRH =$20 ; Note! UCSRC equals UBRRH

.equ EEARH =$1f

.equ EEARL =$1e

.equ EEDR =$1d

.equ EECR =$1c

.equ PORTA =$1b

.equ DDRA =$1a

.equ PINA =$19

.equ PORTB =$18

.equ DDRB =$17

.equ PINB =$16

.equ PORTC =$15

.equ DDRC =$14

.equ PINC =$13

.equ PORTD =$12

.equ DDRD =$11

.equ PIND =$10

.equ SPDR =$0f

.equ SPSR =$0e

.equ SPCR =$0d

.equ UDR =$0c

.equ UCSRA =$0b

.equ UCSRB =$0a

.equ UBRR =$09 ; for AT90S8515

.equ UBRRL =$09

.equ ACSR =$08

.equ PORTE =$07

.equ DDRE =$06

.equ PINE =$05

.equ OSCCAL =$04 ; New

;***** Bit Definitions

;GIMSK

.equ INT1 =7

.equ INT0 =6

.equ INT2 =5

.equ IVSEL =1 ; interrupt vector select

.equ IVCE =0 ; interrupt vector change enable

;GIFR

.equ INTF1 =7

.equ INTF0 =6

.equ INTF2 =5

;TIMSK

.equ TOIE1 =7

.equ OCIE1A =6

.equ OCIE1B =5

.equ TICIE1 =3

.equ TOIE0 =1

.equ OCIE0 =0

;TIFR

.equ TOV1 =7

.equ OCF1A =6

.equ OCF1B =5

.equ ICF1 =3

.equ TOV0 =1

.equ OCF0 =0

;SPMCR

.equ SPMIE =7

.equ RWWSB =6

.equ ASB =6 ; old

.equ RWWSRE =4

.equ ASRE =4 ; old

.equ BLBSET =3

.equ PGWRT =2

.equ PGERS =1

.equ SPMEN =0

;EMCUCR

.equ SM0 =7

.equ SRL2 =6

.equ SRL1 =5

.equ SRL0 =4

.equ SRW01 =3

.equ SRW00 =2

.equ SRW11 =1

.equ ISC2 =0

;MCUCR

.equ SRE =7

.equ SRW =6

.equ SRW10 =6

.equ SE =5

.equ SM =4

.equ SM1 =4

.equ ISC11 =3

.equ ISC10 =2

.equ ISC01 =1

.equ ISC00 =0

;MCUSR

.equ SM2 =5

.equ WDRF =3

.equ BORF =2

.equ EXTRF =1

.equ PORF =0

;TCCR0

.equ FOC0 =7

.equ WGM00 =6

.equ COM01 =5

.equ COM00 =4

.equ WGM01 =3

.equ CS02 =2

.equ CS01 =1

.equ CS00 =0

;TCCR1A

.equ COM1A1 = 7

.equ COM1A0 = 6

.equ COM1B1 = 5

.equ COM1B0 = 4

.equ FOC1A = 3

.equ FOC1B = 2

.equ PWM11 = 1 ; OBSOLETE! Use WGM11

.equ PWM10 = 0 ; OBSOLETE! Use WGM10

.equ WGM11 = 1

.equ WGM10 = 0

;TCCR1B

.equ ICNC1 = 7

.equ ICES1 = 6

.equ CTC11 = 4 ; OBSOLETE! Use WGM13

.equ CTC10 = 3 ; OBSOLETE! Use WGM12

.equ WGM13 = 4

.equ WGM12 = 3

.equ CS12 = 2

.equ CS11 = 1

.equ CS10 = 0

;SFIOR

.equ TSM =7

.equ XMBK =6

.equ XMM2 =5

.equ XMM1 =4

.equ XMM0 =3

.equ PUD =2

.equ PSR10 =0

;WDTCR

.equ WDTOE =4

.equ WDCE =4

.equ WDE =3

.equ WDP2 =2

.equ WDP1 =1

.equ WDP0 =0

;EECR

.equ EERIE =3

.equ EEWEE =2

.equ EEMWE =2

.equ EEWE =1

.equ EERE =0

;PORTA

.equ PA7 =7

.equ PA6 =6

.equ PA5 =5

.equ PA4 =4

.equ PA3 =3

.equ PA2 =2

.equ PA1 =1

.equ PA0 =0

;DDRA

.equ DDA7 =7

.equ DDA6 =6

.equ DDA5 =5

.equ DDA4 =4

.equ DDA3 =3

.equ DDA2 =2

.equ DDA1 =1

.equ DDA0 =0

;PINA

.equ PINA7 =7

.equ PINA6 =6

.equ PINA5 =5

.equ PINA4 =4

.equ PINA3 =3

.equ PINA2 =2

.equ PINA1 =1

.equ PINA0 =0

;PORTB

.equ PB7 =7

.equ PB6 =6

.equ PB5 =5

.equ PB4 =4

.equ PB3 =3

.equ PB2 =2

.equ PB1 =1

.equ PB0 =0

;DDRB

.equ DDB7 =7

.equ DDB6 =6

.equ DDB5 =5

.equ DDB4 =4

.equ DDB3 =3

.equ DDB2 =2

.equ DDB1 =1

.equ DDB0 =0

;PINB

.equ PINB7 =7

.equ PINB6 =6

.equ PINB5 =5

.equ PINB4 =4

.equ PINB3 =3

.equ PINB2 =2

.equ PINB1 =1

.equ PINB0 =0

;PORTC

.equ PC7 =7

.equ PC6 =6

.equ PC5 =5

.equ PC4 =4

.equ PC3 =3

.equ PC2 =2

.equ PC1 =1

.equ PC0 =0

;DDRC

.equ DDC7 =7

.equ DDC6 =6

.equ DDC5 =5

.equ DDC4 =4

.equ DDC3 =3

.equ DDC2 =2

.equ DDC1 =1

.equ DDC0 =0

;PINC

.equ PINC7 =7

.equ PINC6 =6

.equ PINC5 =5

.equ PINC4 =4

.equ PINC3 =3

.equ PINC2 =2

.equ PINC1 =1

.equ PINC0 =0

;PORTD

.equ PD7 =7

.equ PD6 =6

.equ PD5 =5

.equ PD4 =4

.equ PD3 =3

.equ PD2 =2

.equ PD1 =1

.equ PD0 =0

;DDRD

.equ DDD7 =7

.equ DDD6 =6

.equ DDD5 =5

.equ DDD4 =4

.equ DDD3 =3

.equ DDD2 =2

.equ DDD1 =1

.equ DDD0 =0

;PIND

.equ PIND7 =7

.equ PIND6 =6

.equ PIND5 =5

.equ PIND4 =4

.equ PIND3 =3

.equ PIND2 =2

.equ PIND1 =1

.equ PIND0 =0

;PORTE

.equ PE2 =2

.equ PE1 =1

.equ PE0 =0

;DDRE

.equ DDE2 =2

.equ DDE1 =1

.equ DDE0 =0

;PINE

.equ PINE2 =2

.equ PINE1 =1

.equ PINE0 =0

;UCSRA

.equ RXC =7

.equ TXC =6

.equ UDRE =5

.equ FE =4

.equ OR =3 ; old name kept for compatibilty

.equ DOR =3

.equ PE =2

.equ UPE =2

.equ U2X =1

.equ MPCM =0

;UCSRB

.equ RXCIE =7

.equ TXCIE =6

.equ UDRIE =5

.equ RXEN =4

.equ TXEN =3

.equ CHR9 =2 ; old name kept for compatibilty

.equ UCSZ2 =2

.equ RXB8 =1

.equ TXB8 =0

;UCSRC

.equ URSEL =7

.equ UMSEL =6

.equ UPM1 =5

.equ UPM0 =4

.equ USBS =3

.equ UCSZ1 =2

.equ UCSZ0 =1

.equ UCPOL =0

;SPCR

.equ SPIE =7

.equ SPE =6

.equ DORD =5

.equ MSTR =4

.equ CPOL =3

.equ CPHA =2

.equ SPR1 =1

.equ SPR0 =0

;SPSR

.equ SPIF =7

.equ WCOL =6

.equ SPI2X =0

;ACSR

.equ ACD =7

.equ AINBG =6

.equ ACBG =6

.equ ACO =5

.equ ACI =4

.equ ACIE =3

.equ ACIC =2

.equ ACIS1 =1

.equ ACIS0 =0

.def XL =r26

.def XH =r27

.def YL =r28

.def YH =r29

.def ZL =r30

.def ZH =r31

.equ RAMEND =$25F

.equ EEPROMEND = $1FF

.equ FLASHEND = $FFF

; byte groups

; /\/--\/--\/--\

.equ SMALLBOOTSTART =0b00111110000000 ;($0F80) smallest boot block is 128W

.equ SECONDBOOTSTART =0b00111100000000 ;($0F00) 2'nd boot block size is 256W

.equ THIRDBOOTSTART =0b00111000000000 ;($0E00) third boot block size is 512W

.equ LARGEBOOTSTART =0b00110000000000 ;($0C00) largest boot block is 1KW

.equ BOOTSTART =THIRDBOOTSTART ;OBSOLETE!!! kept for compatibility

.equ PAGESIZE =32 ;number of WORDS in a page

.equ INT0addr=$001 ;External Interrupt0 Vector Address

.equ INT1addr=$002 ;External Interrupt1 Vector Address

.equ ICP1addr=$003 ;Input Capture1 Interrupt Vector Address

.equ OC1Aaddr=$004 ;Output Compare1A Interrupt Vector Address

.equ OC1Baddr=$005 ;Output Compare1B Interrupt Vector Address

.equ OVF1addr=$006 ;Overflow1 Interrupt Vector Address

.equ OVF0addr=$007 ;Overflow0 Interrupt Vector Address

.equ SPIaddr =$008 ;SPI Interrupt Vector Address

.equ URXCaddr=$009 ;UART Receive Complete Interrupt Vector Address

.equ UDREaddr=$00a ;UART Data Register Empty Interrupt Vector Address

.equ UTXCaddr=$00b ;UART Transmit Complete Interrupt Vector Address

.equ ACIaddr =$00c ;Analog Comparator Interrupt Vector Address

.equ INT2addr=$00d ;External Interrupt2 Vector Address

.equ OC0addr= $00e ;Output Compare0 Interrupt Vector Address

.equ ERDYaddr=$00f ; EEPROM Interrupt Vector Address

.equ SPMaddr =$010 ; SPM complete Interrupt Vector Address

.equ SPMRaddr =$010 ; SPM complete Interrupt Vector Address

.listmac

.include "macro.asm"

; PMDEmu - AVR based emulator of Czechoslovak microcomputer PMD-85 originally based on I8080

; Copyright (C) 2023 Peter Chrenko <stare********@gmail.com>, Topolcany, Slovakia

; macro.asm

; A0-7 = PORTB

; A8-15 = PORTC

.equ ADDRL = PORTB

.equ ADDRH = PORTC

.equ DATADIR = DDRA

.equ DATAIN = PINA

.equ DATAOUT = PORTA

.equ CONTROLRAM = PORTD

.equ VIDEOPORT = PORTD

; D0-D7 = PORTA(OUTPUT):PINA(INPUT)

; PORT D

; PD0 = KBD_DATA(RXD)(IN)

; PD1 = A18 (OUT)

; PD2 = A17 (OUT)

; PD3 = SRAM/FLASH SELECT (OUT)

; PD4 = KBD_CLK (IN)

; PD5 = BUZZER (OUT)

; PD6 = /WR (OUT)

; PD7 = /RD (OUT)

; PORT E

; PE0 = buzzer

; PE1 = CS1 (WE/slash1)

; PE2 = /OE

.equ MEMWR = PE1

.equ MEMRD = PE2

.equ SOUND = PE0

.equ RAM_SELECT = PD3

;flags

.equ PMD_CY = 0

.equ PMD_P = 2

.equ PMD_AC = 4

.equ PMD_Z = 6

.equ PMD_S = 7

.equ PMD_PSW = 0b00000010 ; empty PSW

.equ ATMEL_C = 0

.equ ATMEL_Z = 1

.equ ATMEL_N = 2

.equ ATMEL_V = 3

.equ ATMEL_S = 4

.equ ATMEL_H = 5

.equ ATMEL_T = 6

.equ ATMEL_I = 7

.macro SELECT_RAM

sbi PORTE,MEMWR ; MEMWR_deactive

cbi DDRD, RAM_SELECT

; PD3 na input -> pull up

cbi PORTE,MEMRD ; MEMRD_active

.endmacro

.macro SELECT_FLASH0

sbi DDRD, RAM_SELECT

cbi PORTD, RAM_SELECT

.endmacro

.macro SELECT_FLASH0_zeroPage

sbi DDRD, RAM_SELECT

out PORTD,_zero

.endmacro

.macro SELECT_FLASH1

sbi PORTE, MEMRD

cbi PORTE, MEMWR

.endmacro

.macro MEMWR_pulse

cbi PORTE,MEMWR

sbi PORTE,MEMWR

.endmacro

.macro MEMRD_active

cbi PORTE,MEMRD

.endmacro

.macro MEMRD_deactive

sbi PORTE,MEMRD

.endmacro

.macro MEMWR_active

cbi PORTE,MEMWR

.endmacro

.macro MEMWR_deactive

sbi PORTE,MEMWR

.endmacro

.macro SEND_SOUND

out PORTE,video_PORTE ; prepared sound port (via T bit) -> out

.endmacro

.macro RESTORE_ZH

ldi ZH, high(i_table)

.endmacro

.macro INX_SP

sub _SPL,_255

sbc _SPH,_255

;sbiw _SPL, low(-1)

.endmacro

.macro DCX_SP

add _SPL,_255

adc _SPH,_255

;sbiw _SPL, 1

.endmacro

; kb_lookup

.equ r0 = 1 ; definition of rows of PMD keyboard

.equ r1 = 2 ; 2nd row

.equ r2 = 4 ; 3rd row

.equ r3 = 8 ; 4th row

.equ r4 = 15 ; 5th row

.equ rx = 0 ; mark - not used key

.def m64 = r0

.def snd_reg = r1

.def portValue = r2

.def D = r3

.def E = r4 ; pair (kbd.asm uses movw)

.def video_PORTE = r5

.def video_SREG = r6

.def mask_register = r7

.def _SPL = r8

.def video_ptr_l = r9

.def _zero = r10

.def _255 = r11

.def C = r12 ; pair

.def B = r13

.def L = r14 ; pair register

.def H = r15

.def clock = r16

.def tmp_reg = r17

.def video_tmp = r18 ; shared

.def bit_position = r18 ; shared video_tmp

.def video_ptr_h = r19

.def A = r20 ; pair register - musnt use ADDIW

.def PSW = r21

.def HiReg = r21

.def snd_reg2 = r22 ; may use addiw _SPL,1

.def cntReg = r22

.def _SPH = r23

.def _PCL = r24

.def _PCH = r25

.def snd_pointerWR_lo = r26 ;XL

.def snd_pointerWR_hi = r27 ;XH

.def snd_pointerRD_lo = r28 ; YL

.def snd_pointerRD_hi = r29 ; YH

.def video_tmp2 = r29 ; shared

; Z is used by IJMP & LPM

; Z = 30:31

; Y = 29:28

; X = 27:26

.equ kbd_portC = EEARL

.equ last_result = EEDR

.equ STACK_MAX = 80

.dseg

000060 stack: .byte 160

stack_top:

000100 snd_buffer: .byte 0x100

000200 kb_cols: .byte 16 ; PMDs keyboard has 16 columns selected by 74154

000210 kb_cols_real: .byte 16 ; real PMD85 scanning

000220 blink_counter: .byte 1

000221 kbd_ports: .byte 4 ; keyboard 8255 state

000225 mgf_pointer: .byte 3 ; 3 bytes counter

000228 mgf_header: .byte 1

000229 _rom: .byte 4 ; external ROM modul 8255 state

00022d stop_flag: .byte 1

00022e pmd_version: .byte 1

00022f test_clock: .byte 1

000230 stack_pointer: .byte 1

000231 usart_cw_last: .byte 1

000232 kbd_flags: .byte 1 ; flags for KBD module

; 7 = F0

; 6 = STOP

; 5 = SHIFT

; 4 = ALT

; 3 =

; 2 =

; 1 =

; 0 =

.equ F0_bit = 7

.equ STOP_bit = 6

.equ SHIFT_bit = 5

.equ ALT_bit = 4

.cseg

.org 0

; use some bytes of memory to inicialization

000000 24aa clr _zero ; _zero := 0

000001 efef ldi r30,255

000002 2ebe mov _255,r30

000003 bab7 out DDRB,_255 ; portB vystup (address)

000004 c5bd rjmp after_reset

; PMDEmu - AVR based emulator of Czechoslo vak microcomputer PMD-85 originally based on I8080

; Copyright (C) 2023 Peter Chrenko <stare********@gmail.com>, Topolcany, Slovakia

; video.php

.equ total_lines = 312

.equ visible_lines = 256

.equ dark_lines = 36

.equ vsync_lines = 5

.equ lines1 = 31

.equ lines2 = 51

.equ lines3 = 56

.equ VIDEO_SOUND = 0x80

.equ VIDEO_BIT7_LINE=0x9b

.macro TIMER0_START

out TCNT0,_zero

ldi video_tmp, 0b00001001 ; run TCCR0 at CLK, CTC mode 2

out TCCR0, video_tmp

.endmacro

.macro TIMER0_STOP

out TCCR0,_zero

.endmacro

.org OC1Baddr

interrupt_OCR1B:

000005 b66f in video_SREG,SREG

000006 fa10 bst snd_reg,0

000007 f850 bld video_PORTE,SOUND

000008 + SEND_SOUND

000008 b857 out PORTE,video_PORTE ; prepared sound port (via T bit) -> out

.endmacro

000009 c020 rjmp OCR1B_continue

.org OC0addr

00000e b66f in video_SREG,SREG

00000f 3027 cpi bit_position,7

000010 f440 brsh bit7

000011 9415 asr snd_reg

000012 fa10 bst snd_reg,0

000013 b1d7 in video_tmp2,PORTE

000014 f9d0 bld video_tmp2, SOUND

000015 b9d7 out PORTE,video_tmp2

000016 9523 inc bit_position

000017 be6f out SREG,video_SREG

000018 9518 reti

bit7:

000019 + TIMER0_STOP

000019 bea3 out TCCR0,_zero

.endmacro

00001a fa17 bst snd_reg,7

00001b b1d7 in video_tmp2,PORTE

00001c f9d0 bld video_tmp2, SOUND

00001d b9d7 out PORTE,video_tmp2

00001e e0d1 ldi snd_pointerRD_hi, high(snd_buffer)

00001f 9019 ld snd_reg, Y+ ; increment is modulo 256, snd_pointerRD_hi is always const

000020 b3de in video_tmp2, kbd_portC ; PC

000021 30d0 cpi video_tmp2, 0

000022 f029 breq snd_cnt

000023 2c1b mov snd_reg,_255

000024 9403 inc m64

000025 21d0 and video_tmp2, m64

000026 11da cpse video_tmp2, _zero

000027 2c1a mov snd_reg,_zero

snd_cnt:

000028 be6f out SREG,video_SREG

000029 9518 reti

OCR1B_continue:

00002a 3c30 cpi video_ptr_h, 0xc0 ;line 31

00002b f518 brsh normal_line

00002c 9533 inc video_ptr_h

00002d + TIMER0_START

00002d bea2 out TCNT0,_zero

00002e e029 ldi video_tmp, 0b00001001 ; run TCCR0 at CLK, CTC mode 2

00002f bf23 out TCCR0, video_tmp

.endmacro

000030 3134 cpi video_ptr_h, 20 ;51

000031 f079 breq vertical_sync_begin

000032 3139 cpi video_ptr_h, 25 ;56

000033 f0a1 breq vertical_sync_end

000034 3337 cpi video_ptr_h, 55 ;56

000035 f449 brne return_sync

; setup "videoprocessor" position to left upper corner

; video address := 0xc000

000036 ec30 ldi video_ptr_h,0xc0

000037 9120 0220 lds video_tmp,blink_counter

000039 952a dec video_tmp

00003a f411 brne no_visibility_change

00003b 9470 com mask_register

00003c e322 ldi video_tmp,blink_period

no_visibility_change:

00003d 9320 0220 sts blink_counter,video_tmp

return_sync:

00003f e021 ldi bit_position,1

000040 c3a3 rjmp _reti

vertical_sync_begin: ; first vertical sync signal

000041 ec22 ldi video_tmp,0b11000010

000042 bd2f out TCCR1A,video_tmp ; negacia

000043 e022 ldi video_tmp,high(590) ; when sync goes low

000044 bd2b out OCR1AH,video_tmp ; channel T1/A

000045 e42e ldi video_tmp,low(590)

000046 bd2a out OCR1AL,video_tmp

000047 cff7 rjmp return_sync

vertical_sync_end: ; last vertical sync signal

000048 e822 ldi video_tmp,0b10000010

000049 bd2f out TCCR1A,video_tmp

00004a e024 ldi video_tmp,high(1097) ; when sync goes low

00004b bd2b out OCR1AH,video_tmp ; channel T1/A

00004c e429 ldi video_tmp,low(1097)

00004d bd2a out OCR1AL,video_tmp

00004e cff0 rjmp return_sync

normal_line:

; show TV microline

00004f b328 in video_tmp,ADDRL

000050 932f push video_tmp

000051 b325 in video_tmp,ADDRH

000052 932f push video_tmp

000053 ba98 out ADDRL,video_ptr_l

000054 bb35 out ADDRH,video_ptr_h

000055 b52c in video_tmp,TCNT1L ;synchronize with 1 and 2 cycles interrupted instuction

000056 ff20 sbrs video_tmp,0

000057 c000 rjmp PC+1

000058 b329 in video_tmp,PINA ; B X 5 4 3 2 1 0 (B = blink, X = not implemented)

000059 fd27 sbrc video_tmp,7 ;

00005a 2127 and video_tmp,mask_register

00005b 0f22 lsl video_tmp

; 0. byte

00005c bb22 out VIDEOPORT,video_tmp ; 0.bit first byte

00005d 9525 asr video_tmp

00005e 9493 inc video_ptr_l

00005f bb22 out VIDEOPORT,video_tmp ; 1.bit first byte

000060 9525 asr video_tmp

000061 ba98 out ADDRL,video_ptr_l ; output low address

000062 bb22 out VIDEOPORT,video_tmp ; 2.bit first byte

000063 9525 asr video_tmp

000064 b3d9 in video_tmp2,PINA ; load next 6 pixels :X X 5 4 3 2 1 0

000065 bb22 out VIDEOPORT,video_tmp ; 3.bit first byte

000066 9525 asr video_tmp

000067 0000 nop ; ========= BITSOUND (NOP) ===

000068 bb22 out VIDEOPORT,video_tmp ; 4.bit first byte

000069 9525 asr video_tmp

00006a 0fdd lsl video_tmp2

00006b bb22 out VIDEOPORT,video_tmp ; 5.bit first byte

00006c f408 brcc pc+2

00006d 21d7 and video_tmp2,mask_register

; 1.byte

00006e bbd2 out VIDEOPORT,video_tmp2 ; 0.bit second byte

00006f 95d5 asr video_tmp2

000070 9493 inc video_ptr_l

000071 bbd2 out VIDEOPORT,video_tmp2 ; 1.bit second byte

000072 95d5 asr video_tmp2

000073 ba98 out ADDRL,video_ptr_l ; output low address

000074 bbd2 out VIDEOPORT,video_tmp2 ; 2.bit second byte

000075 95d5 asr video_tmp2

000076 b329 in video_tmp,PINA ; load next 6 pixels :X X 5 4 3 2 1 0

000077 bbd2 out VIDEOPORT,video_tmp2 ; 3.bit second byte

000078 95d5 asr video_tmp2

000079 0000 nop ; ========= BITSOUND (NOP) ===

00007a bbd2 out VIDEOPORT,video_tmp2 ; 4.bit second byte

00007b 95d5 asr video_tmp2

00007c 0f22 lsl video_tmp

00007d bbd2 out VIDEOPORT,video_tmp2 ; 5.bit second byte

00007e f408 brcc pc+2

00007f 2127 and video_tmp,mask_register

; 2. byte

000080 bb22 out VIDEOPORT,video_tmp ; 0.bit first byte

000081 9525 asr video_tmp

000082 9493 inc video_ptr_l

000083 bb22 out VIDEOPORT,video_tmp ; 1.bit first byte

000084 9525 asr video_tmp

000085 ba98 out ADDRL,video_ptr_l ; output low address

000086 bb22 out VIDEOPORT,video_tmp ; 2.bit first byte

000087 9525 asr video_tmp

000088 b3d9 in video_tmp2,PINA ; load next 6 pixels :X X 5 4 3 2 1 0

000089 bb22 out VIDEOPORT,video_tmp ; 3.bit first byte

00008a 9525 asr video_tmp

00008b 0000 nop ; ========= BITSOUND (NOP) ===

00008c bb22 out VIDEOPORT,video_tmp ; 4.bit first byte

00008d 9525 asr video_tmp

00008e 0fdd lsl video_tmp2

00008f bb22 out VIDEOPORT,video_tmp ; 5.bit first byte

000090 f408 brcc pc+2

000091 21d7 and video_tmp2,mask_register

; 3.byte

000092 bbd2 out VIDEOPORT,video_tmp2 ; 0.bit second byte

000093 95d5 asr video_tmp2

000094 9493 inc video_ptr_l

000095 bbd2 out VIDEOPORT,video_tmp2 ; 1.bit second byte

000096 95d5 asr video_tmp2

000097 ba98 out ADDRL,video_ptr_l ; output low address

000098 bbd2 out VIDEOPORT,video_tmp2 ; 2.bit second byte

000099 95d5 asr video_tmp2

00009a b329 in video_tmp,PINA ; load next 6 pixels :X X 5 4 3 2 1 0

00009b bbd2 out VIDEOPORT,video_tmp2 ; 3.bit second byte

00009c 95d5 asr video_tmp2

00009d 0000 nop ; ========= BITSOUND (NOP) ===

00009e bbd2 out VIDEOPORT,video_tmp2 ; 4.bit second byte

00009f 95d5 asr video_tmp2

0000a0 0f22 lsl video_tmp

0000a1 bbd2 out VIDEOPORT,video_tmp2 ; 5.bit second byte

0000a2 f408 brcc pc+2

0000a3 2127 and video_tmp,mask_register

; 4. byte

0000a4 bb22 out VIDEOPORT,video_tmp ; 0.bit first byte

0000a5 9525 asr video_tmp

0000a6 9493 inc video_ptr_l

0000a7 bb22 out VIDEOPORT,video_tmp ; 1.bit first byte

0000a8 9525 asr video_tmp

0000a9 ba98 out ADDRL,video_ptr_l ; output low address

0000aa bb22 out VIDEOPORT,video_tmp ; 2.bit first byte

0000ab 9525 asr video_tmp

0000ac b3d9 in video_tmp2,PINA ; load next 6 pixels :X X 5 4 3 2 1 0

0000ad bb22 out VIDEOPORT,video_tmp ; 3.bit first byte

0000ae 9525 asr video_tmp

0000af 0000 nop ; ========= BITSOUND (NOP) ===

0000b0 bb22 out VIDEOPORT,video_tmp ; 4.bit first byte

0000b1 9525 asr video_tmp

0000b2 0fdd lsl video_tmp2

0000b3 bb22 out VIDEOPORT,video_tmp ; 5.bit first byte

0000b4 f408 brcc pc+2

0000b5 21d7 and video_tmp2,mask_register

; 5.byte

0000b6 bbd2 out VIDEOPORT,video_tmp2 ; 0.bit second byte

0000b7 95d5 asr video_tmp2

0000b8 9493 inc video_ptr_l

0000b9 bbd2 out VIDEOPORT,video_tmp2 ; 1.bit second byte

0000ba 95d5 asr video_tmp2

0000bb ba98 out ADDRL,video_ptr_l ; output low address

0000bc bbd2 out VIDEOPORT,video_tmp2 ; 2.bit second byte

0000bd 95d5 asr video_tmp2

0000be b329 in video_tmp,PINA ; load next 6 pixels :X X 5 4 3 2 1 0

0000bf bbd2 out VIDEOPORT,video_tmp2 ; 3.bit second byte

0000c0 95d5 asr video_tmp2

0000c1 fa11 bst snd_reg, 1 ; ========= BITSOUND (OP1: BIT 1) ===

0000c2 bbd2 out VIDEOPORT,video_tmp2 ; 4.bit second byte

0000c3 95d5 asr video_tmp2

0000c4 0f22 lsl video_tmp

0000c5 bbd2 out VIDEOPORT,video_tmp2 ; 5.bit second byte

0000c6 f408 brcc pc+2

0000c7 2127 and video_tmp,mask_register

; 6. byte

0000c8 bb22 out VIDEOPORT,video_tmp ; 0.bit first byte

0000c9 9525 asr video_tmp

0000ca 9493 inc video_ptr_l

0000cb bb22 out VIDEOPORT,video_tmp ; 1.bit first byte

0000cc 9525 asr video_tmp

0000cd ba98 out ADDRL,video_ptr_l ; output low address

0000ce bb22 out VIDEOPORT,video_tmp ; 2.bit first byte

0000cf 9525 asr video_tmp

0000d0 b3d9 in video_tmp2,PINA ; load next 6 pixels :X X 5 4 3 2 1 0

0000d1 bb22 out VIDEOPORT,video_tmp ; 3.bit first byte

0000d2 9525 asr video_tmp

0000d3 f850 bld video_PORTE,SOUND ; ========= BITSOUND (OP2: BIT 1) ===

0000d4 bb22 out VIDEOPORT,video_tmp ; 4.bit first byte

0000d5 9525 asr video_tmp

0000d6 0fdd lsl video_tmp2

0000d7 bb22 out VIDEOPORT,video_tmp ; 5.bit first byte

0000d8 f408 brcc pc+2

0000d9 21d7 and video_tmp2,mask_register

; 7.byte

0000da bbd2 out VIDEOPORT,video_tmp2 ; 0.bit second byte

0000db 95d5 asr video_tmp2

0000dc 9493 inc video_ptr_l

0000dd bbd2 out VIDEOPORT,video_tmp2 ; 1.bit second byte

0000de 95d5 asr video_tmp2

0000df ba98 out ADDRL,video_ptr_l ; output low address

0000e0 bbd2 out VIDEOPORT,video_tmp2 ; 2.bit second byte

0000e1 95d5 asr video_tmp2

0000e2 b329 in video_tmp,PINA ; load next 6 pixels :X X 5 4 3 2 1 0

0000e3 bbd2 out VIDEOPORT,video_tmp2 ; 3.bit second byte

0000e4 95d5 asr video_tmp2

0000e5 + SEND_SOUND ; ========= BITSOUND (OP3: BIT 1) ===

0000e5 b857 out PORTE,video_PORTE ; prepared sound port (via T bit) -> out

.endmacro

0000e6 bbd2 out VIDEOPORT,video_tmp2 ; 4.bit second byte

0000e7 95d5 asr video_tmp2

0000e8 0f22 lsl video_tmp

0000e9 bbd2 out VIDEOPORT,video_tmp2 ; 5.bit second byte

0000ea f408 brcc pc+2

0000eb 2127 and video_tmp,mask_register

; 8. byte

0000ec bb22 out VIDEOPORT,video_tmp ; 0.bit first byte

0000ed 9525 asr video_tmp

0000ee 9493 inc video_ptr_l

0000ef bb22 out VIDEOPORT,video_tmp ; 1.bit first byte

0000f0 9525 asr video_tmp

0000f1 ba98 out ADDRL,video_ptr_l ; output low address

0000f2 bb22 out VIDEOPORT,video_tmp ; 2.bit first byte

0000f3 9525 asr video_tmp

0000f4 b3d9 in video_tmp2,PINA ; load next 6 pixels :X X 5 4 3 2 1 0

0000f5 bb22 out VIDEOPORT,video_tmp ; 3.bit first byte

0000f6 9525 asr video_tmp

0000f7 0000 nop ; ========= BITSOUND (NOP) ===

0000f8 bb22 out VIDEOPORT,video_tmp ; 4.bit first byte

0000f9 9525 asr video_tmp

0000fa 0fdd lsl video_tmp2

0000fb bb22 out VIDEOPORT,video_tmp ; 5.bit first byte

0000fc f408 brcc pc+2

0000fd 21d7 and video_tmp2,mask_register

; 9.byte

0000fe bbd2 out VIDEOPORT,video_tmp2 ; 0.bit second byte

0000ff 95d5 asr video_tmp2

000100 9493 inc video_ptr_l

000101 bbd2 out VIDEOPORT,video_tmp2 ; 1.bit second byte

000102 95d5 asr video_tmp2

000103 ba98 out ADDRL,video_ptr_l ; output low address

000104 bbd2 out VIDEOPORT,video_tmp2 ; 2.bit second byte

000105 95d5 asr video_tmp2

000106 b329 in video_tmp,PINA ; load next 6 pixels :X X 5 4 3 2 1 0

000107 bbd2 out VIDEOPORT,video_tmp2 ; 3.bit second byte

000108 95d5 asr video_tmp2

000109 0000 nop ; ========= BITSOUND (NOP) ===

00010a bbd2 out VIDEOPORT,video_tmp2 ; 4.bit second byte

00010b 95d5 asr video_tmp2

00010c 0f22 lsl video_tmp

00010d bbd2 out VIDEOPORT,video_tmp2 ; 5.bit second byte

00010e f408 brcc pc+2

00010f 2127 and video_tmp,mask_register

; 10. byte

000110 bb22 out VIDEOPORT,video_tmp ; 0.bit first byte

000111 9525 asr video_tmp

000112 9493 inc video_ptr_l

000113 bb22 out VIDEOPORT,video_tmp ; 1.bit first byte

000114 9525 asr video_tmp

000115 ba98 out ADDRL,video_ptr_l ; output low address

000116 bb22 out VIDEOPORT,video_tmp ; 2.bit first byte

000117 9525 asr video_tmp

000118 b3d9 in video_tmp2,PINA ; load next 6 pixels :X X 5 4 3 2 1 0

000119 bb22 out VIDEOPORT,video_tmp ; 3.bit first byte

00011a 9525 asr video_tmp

00011b 0000 nop ; ========= BITSOUND (NOP) ===

00011c bb22 out VIDEOPORT,video_tmp ; 4.bit first byte

00011d 9525 asr video_tmp

00011e 0fdd lsl video_tmp2

00011f bb22 out VIDEOPORT,video_tmp ; 5.bit first byte

000120 f408 brcc pc+2

000121 21d7 and video_tmp2,mask_register

; 11.byte

000122 bbd2 out VIDEOPORT,video_tmp2 ; 0.bit second byte

000123 95d5 asr video_tmp2

000124 9493 inc video_ptr_l

000125 bbd2 out VIDEOPORT,video_tmp2 ; 1.bit second byte

000126 95d5 asr video_tmp2

000127 ba98 out ADDRL,video_ptr_l ; output low address

000128 bbd2 out VIDEOPORT,video_tmp2 ; 2.bit second byte

000129 95d5 asr video_tmp2

00012a b329 in video_tmp,PINA ; load next 6 pixels :X X 5 4 3 2 1 0

00012b bbd2 out VIDEOPORT,video_tmp2 ; 3.bit second byte

00012c 95d5 asr video_tmp2

00012d 0000 nop ; ========= BITSOUND (NOP) ===

00012e bbd2 out VIDEOPORT,video_tmp2 ; 4.bit second byte

00012f 95d5 asr video_tmp2

000130 0f22 lsl video_tmp

000131 bbd2 out VIDEOPORT,video_tmp2 ; 5.bit second byte

000132 f408 brcc pc+2

000133 2127 and video_tmp,mask_register

; 12. byte

000134 bb22 out VIDEOPORT,video_tmp ; 0.bit first byte

000135 9525 asr video_tmp

000136 9493 inc video_ptr_l

000137 bb22 out VIDEOPORT,video_tmp ; 1.bit first byte

000138 9525 asr video_tmp

000139 ba98 out ADDRL,video_ptr_l ; output low address

00013a bb22 out VIDEOPORT,video_tmp ; 2.bit first byte

00013b 9525 asr video_tmp

00013c b3d9 in video_tmp2,PINA ; load next 6 pixels :X X 5 4 3 2 1 0

00013d bb22 out VIDEOPORT,video_tmp ; 3.bit first byte

00013e 9525 asr video_tmp

00013f 0000 nop ; ========= BITSOUND (NOP) ===

000140 bb22 out VIDEOPORT,video_tmp ; 4.bit first byte

000141 9525 asr video_tmp

000142 0fdd lsl video_tmp2

000143 bb22 out VIDEOPORT,video_tmp ; 5.bit first byte

000144 f408 brcc pc+2

000145 21d7 and video_tmp2,mask_register

; 13.byte

000146 bbd2 out VIDEOPORT,video_tmp2 ; 0.bit second byte

000147 95d5 asr video_tmp2

000148 9493 inc video_ptr_l

000149 bbd2 out VIDEOPORT,video_tmp2 ; 1.bit second byte

00014a 95d5 asr video_tmp2

00014b ba98 out ADDRL,video_ptr_l ; output low address

00014c bbd2 out VIDEOPORT,video_tmp2 ; 2.bit second byte

00014d 95d5 asr video_tmp2

00014e b329 in video_tmp,PINA ; load next 6 pixels :X X 5 4 3 2 1 0

00014f bbd2 out VIDEOPORT,video_tmp2 ; 3.bit second byte

000150 95d5 asr video_tmp2

000151 fa12 bst snd_reg, 2 ; ========= BITSOUND (OP1: BIT 2) ===

000152 bbd2 out VIDEOPORT,video_tmp2 ; 4.bit second byte

000153 95d5 asr video_tmp2

000154 0f22 lsl video_tmp

000155 bbd2 out VIDEOPORT,video_tmp2 ; 5.bit second byte

000156 f408 brcc pc+2

000157 2127 and video_tmp,mask_register

; 14. byte

000158 bb22 out VIDEOPORT,video_tmp ; 0.bit first byte

000159 9525 asr video_tmp

00015a 9493 inc video_ptr_l

00015b bb22 out VIDEOPORT,video_tmp ; 1.bit first byte

00015c 9525 asr video_tmp

00015d ba98 out ADDRL,video_ptr_l ; output low address

00015e bb22 out VIDEOPORT,video_tmp ; 2.bit first byte

00015f 9525 asr video_tmp

000160 b3d9 in video_tmp2,PINA ; load next 6 pixels :X X 5 4 3 2 1 0

000161 bb22 out VIDEOPORT,video_tmp ; 3.bit first byte

000162 9525 asr video_tmp

000163 f850 bld video_PORTE,SOUND ; ========= BITSOUND (OP2: BIT 2) ===

000164 bb22 out VIDEOPORT,video_tmp ; 4.bit first byte

000165 9525 asr video_tmp

000166 0fdd lsl video_tmp2

000167 bb22 out VIDEOPORT,video_tmp ; 5.bit first byte

000168 f408 brcc pc+2

000169 21d7 and video_tmp2,mask_register

; 15.byte

00016a bbd2 out VIDEOPORT,video_tmp2 ; 0.bit second byte

00016b 95d5 asr video_tmp2

00016c 9493 inc video_ptr_l

00016d bbd2 out VIDEOPORT,video_tmp2 ; 1.bit second byte

00016e 95d5 asr video_tmp2

00016f ba98 out ADDRL,video_ptr_l ; output low address

000170 bbd2 out VIDEOPORT,video_tmp2 ; 2.bit second byte

000171 95d5 asr video_tmp2

000172 b329 in video_tmp,PINA ; load next 6 pixels :X X 5 4 3 2 1 0

000173 bbd2 out VIDEOPORT,video_tmp2 ; 3.bit second byte

000174 95d5 asr video_tmp2

000175 + SEND_SOUND ; ========= BITSOUND (OP3: BIT 2) ===

000175 b857 out PORTE,video_PORTE ; prepared sound port (via T bit) -> out

.endmacro

000176 bbd2 out VIDEOPORT,video_tmp2 ; 4.bit second byte

000177 95d5 asr video_tmp2

000178 0f22 lsl video_tmp

000179 bbd2 out VIDEOPORT,video_tmp2 ; 5.bit second byte

00017a f408 brcc pc+2

00017b 2127 and video_tmp,mask_register

; 16. byte

00017c bb22 out VIDEOPORT,video_tmp ; 0.bit first byte

00017d 9525 asr video_tmp

00017e 9493 inc video_ptr_l

00017f bb22 out VIDEOPORT,video_tmp ; 1.bit first byte

000180 9525 asr video_tmp

000181 ba98 out ADDRL,video_ptr_l ; output low address

000182 bb22 out VIDEOPORT,video_tmp ; 2.bit first byte

000183 9525 asr video_tmp

000184 b3d9 in video_tmp2,PINA ; load next 6 pixels :X X 5 4 3 2 1 0

000185 bb22 out VIDEOPORT,video_tmp ; 3.bit first byte

000186 9525 asr video_tmp

000187 0000 nop ; ========= BITSOUND (NOP) ===

000188 bb22 out VIDEOPORT,video_tmp ; 4.bit first byte

000189 9525 asr video_tmp

00018a 0fdd lsl video_tmp2

00018b bb22 out VIDEOPORT,video_tmp ; 5.bit first byte

00018c f408 brcc pc+2

00018d 21d7 and video_tmp2,mask_register

; 17.byte

00018e bbd2 out VIDEOPORT,video_tmp2 ; 0.bit second byte

00018f 95d5 asr video_tmp2

000190 9493 inc video_ptr_l

000191 bbd2 out VIDEOPORT,video_tmp2 ; 1.bit second byte

000192 95d5 asr video_tmp2

000193 ba98 out ADDRL,video_ptr_l ; output low address

000194 bbd2 out VIDEOPORT,video_tmp2 ; 2.bit second byte

000195 95d5 asr video_tmp2

000196 b329 in video_tmp,PINA ; load next 6 pixels :X X 5 4 3 2 1 0

000197 bbd2 out VIDEOPORT,video_tmp2 ; 3.bit second byte

000198 95d5 asr video_tmp2

000199 0000 nop ; ========= BITSOUND (NOP) ===

00019a bbd2 out VIDEOPORT,video_tmp2 ; 4.bit second byte

00019b 95d5 asr video_tmp2

00019c 0f22 lsl video_tmp

00019d bbd2 out VIDEOPORT,video_tmp2 ; 5.bit second byte

00019e f408 brcc pc+2

00019f 2127 and video_tmp,mask_register

; 18. byte

0001a0 bb22 out VIDEOPORT,video_tmp ; 0.bit first byte

0001a1 9525 asr video_tmp

0001a2 9493 inc video_ptr_l

0001a3 bb22 out VIDEOPORT,video_tmp ; 1.bit first byte

0001a4 9525 asr video_tmp

0001a5 ba98 out ADDRL,video_ptr_l ; output low address

0001a6 bb22 out VIDEOPORT,video_tmp ; 2.bit first byte

0001a7 9525 asr video_tmp

0001a8 b3d9 in video_tmp2,PINA ; load next 6 pixels :X X 5 4 3 2 1 0

0001a9 bb22 out VIDEOPORT,video_tmp ; 3.bit first byte

0001aa 9525 asr video_tmp

0001ab 0000 nop ; ========= BITSOUND (NOP) ===

0001ac bb22 out VIDEOPORT,video_tmp ; 4.bit first byte

0001ad 9525 asr video_tmp

0001ae 0fdd lsl video_tmp2

0001af bb22 out VIDEOPORT,video_tmp ; 5.bit first byte

0001b0 f408 brcc pc+2

0001b1 21d7 and video_tmp2,mask_register

; 19.byte

0001b2 bbd2 out VIDEOPORT,video_tmp2 ; 0.bit second byte

0001b3 95d5 asr video_tmp2

0001b4 9493 inc video_ptr_l

0001b5 bbd2 out VIDEOPORT,video_tmp2 ; 1.bit second byte

0001b6 95d5 asr video_tmp2

0001b7 ba98 out ADDRL,video_ptr_l ; output low address

0001b8 bbd2 out VIDEOPORT,video_tmp2 ; 2.bit second byte

0001b9 95d5 asr video_tmp2

0001ba b329 in video_tmp,PINA ; load next 6 pixels :X X 5 4 3 2 1 0

0001bb bbd2 out VIDEOPORT,video_tmp2 ; 3.bit second byte

0001bc 95d5 asr video_tmp2

0001bd 0000 nop ; ========= BITSOUND (NOP) ===

0001be bbd2 out VIDEOPORT,video_tmp2 ; 4.bit second byte

0001bf 95d5 asr video_tmp2

0001c0 0f22 lsl video_tmp

0001c1 bbd2 out VIDEOPORT,video_tmp2 ; 5.bit second byte

0001c2 f408 brcc pc+2

0001c3 2127 and video_tmp,mask_register

; 20. byte

0001c4 bb22 out VIDEOPORT,video_tmp ; 0.bit first byte

0001c5 9525 asr video_tmp

0001c6 9493 inc video_ptr_l

0001c7 bb22 out VIDEOPORT,video_tmp ; 1.bit first byte

0001c8 9525 asr video_tmp

0001c9 ba98 out ADDRL,video_ptr_l ; output low address

0001ca bb22 out VIDEOPORT,video_tmp ; 2.bit first byte

0001cb 9525 asr video_tmp

0001cc b3d9 in video_tmp2,PINA ; load next 6 pixels :X X 5 4 3 2 1 0

0001cd bb22 out VIDEOPORT,video_tmp ; 3.bit first byte

0001ce 9525 asr video_tmp

0001cf 0000 nop ; ========= BITSOUND (NOP) ===

0001d0 bb22 out VIDEOPORT,video_tmp ; 4.bit first byte

0001d1 9525 asr video_tmp

0001d2 0fdd lsl video_tmp2

0001d3 bb22 out VIDEOPORT,video_tmp ; 5.bit first byte

0001d4 f408 brcc pc+2

0001d5 21d7 and video_tmp2,mask_register

; 21.byte

0001d6 bbd2 out VIDEOPORT,video_tmp2 ; 0.bit second byte

0001d7 95d5 asr video_tmp2

0001d8 9493 inc video_ptr_l

0001d9 bbd2 out VIDEOPORT,video_tmp2 ; 1.bit second byte

0001da 95d5 asr video_tmp2

0001db ba98 out ADDRL,video_ptr_l ; output low address

0001dc bbd2 out VIDEOPORT,video_tmp2 ; 2.bit second byte

0001dd 95d5 asr video_tmp2

0001de b329 in video_tmp,PINA ; load next 6 pixels :X X 5 4 3 2 1 0

0001df bbd2 out VIDEOPORT,video_tmp2 ; 3.bit second byte

0001e0 95d5 asr video_tmp2

0001e1 fa13 bst snd_reg, 3 ; ========= BITSOUND (OP1: BIT 3) ===

0001e2 bbd2 out VIDEOPORT,video_tmp2 ; 4.bit second byte

0001e3 95d5 asr video_tmp2

0001e4 0f22 lsl video_tmp

0001e5 bbd2 out VIDEOPORT,video_tmp2 ; 5.bit second byte

0001e6 f408 brcc pc+2

0001e7 2127 and video_tmp,mask_register

; 22. byte

0001e8 bb22 out VIDEOPORT,video_tmp ; 0.bit first byte

0001e9 9525 asr video_tmp

0001ea 9493 inc video_ptr_l

0001eb bb22 out VIDEOPORT,video_tmp ; 1.bit first byte

0001ec 9525 asr video_tmp

0001ed ba98 out ADDRL,video_ptr_l ; output low address

0001ee bb22 out VIDEOPORT,video_tmp ; 2.bit first byte

0001ef 9525 asr video_tmp

0001f0 b3d9 in video_tmp2,PINA ; load next 6 pixels :X X 5 4 3 2 1 0

0001f1 bb22 out VIDEOPORT,video_tmp ; 3.bit first byte

0001f2 9525 asr video_tmp

0001f3 f850 bld video_PORTE,SOUND ; ========= BITSOUND (OP2: BIT 3) ===

0001f4 bb22 out VIDEOPORT,video_tmp ; 4.bit first byte

0001f5 9525 asr video_tmp

0001f6 0fdd lsl video_tmp2

0001f7 bb22 out VIDEOPORT,video_tmp ; 5.bit first byte

0001f8 f408 brcc pc+2

0001f9 21d7 and video_tmp2,mask_register

; 23.byte

0001fa bbd2 out VIDEOPORT,video_tmp2 ; 0.bit second byte

0001fb 95d5 asr video_tmp2

0001fc 9493 inc video_ptr_l

0001fd bbd2 out VIDEOPORT,video_tmp2 ; 1.bit second byte

0001fe 95d5 asr video_tmp2

0001ff ba98 out ADDRL,video_ptr_l ; output low address

000200 bbd2 out VIDEOPORT,video_tmp2 ; 2.bit second byte

000201 95d5 asr video_tmp2

000202 b329 in video_tmp,PINA ; load next 6 pixels :X X 5 4 3 2 1 0

000203 bbd2 out VIDEOPORT,video_tmp2 ; 3.bit second byte

000204 95d5 asr video_tmp2

000205 + SEND_SOUND ; ========= BITSOUND (OP3: BIT 3) ===

000205 b857 out PORTE,video_PORTE ; prepared sound port (via T bit) -> out

.endmacro

000206 bbd2 out VIDEOPORT,video_tmp2 ; 4.bit second byte

000207 95d5 asr video_tmp2

000208 0f22 lsl video_tmp

000209 bbd2 out VIDEOPORT,video_tmp2 ; 5.bit second byte

00020a f408 brcc pc+2

00020b 2127 and video_tmp,mask_register

; 24. byte

00020c bb22 out VIDEOPORT,video_tmp ; 0.bit first byte

00020d 9525 asr video_tmp

00020e 9493 inc video_ptr_l

00020f bb22 out VIDEOPORT,video_tmp ; 1.bit first byte

000210 9525 asr video_tmp

000211 ba98 out ADDRL,video_ptr_l ; output low address

000212 bb22 out VIDEOPORT,video_tmp ; 2.bit first byte

000213 9525 asr video_tmp

000214 b3d9 in video_tmp2,PINA ; load next 6 pixels :X X 5 4 3 2 1 0

000215 bb22 out VIDEOPORT,video_tmp ; 3.bit first byte

000216 9525 asr video_tmp

000217 0000 nop ; ========= BITSOUND (NOP) ===

000218 bb22 out VIDEOPORT,video_tmp ; 4.bit first byte

000219 9525 asr video_tmp

00021a 0fdd lsl video_tmp2

00021b bb22 out VIDEOPORT,video_tmp ; 5.bit first byte

00021c f408 brcc pc+2

00021d 21d7 and video_tmp2,mask_register

; 25.byte

00021e bbd2 out VIDEOPORT,video_tmp2 ; 0.bit second byte

00021f 95d5 asr video_tmp2

000220 9493 inc video_ptr_l

000221 bbd2 out VIDEOPORT,video_tmp2 ; 1.bit second byte

000222 95d5 asr video_tmp2

000223 ba98 out ADDRL,video_ptr_l ; output low address

000224 bbd2 out VIDEOPORT,video_tmp2 ; 2.bit second byte

000225 95d5 asr video_tmp2

000226 b329 in video_tmp,PINA ; load next 6 pixels :X X 5 4 3 2 1 0

000227 bbd2 out VIDEOPORT,video_tmp2 ; 3.bit second byte

000228 95d5 asr video_tmp2

000229 0000 nop ; ========= BITSOUND (NOP) ===

00022a bbd2 out VIDEOPORT,video_tmp2 ; 4.bit second byte

00022b 95d5 asr video_tmp2

00022c 0f22 lsl video_tmp

00022d bbd2 out VIDEOPORT,video_tmp2 ; 5.bit second byte

00022e f408 brcc pc+2

00022f 2127 and video_tmp,mask_register

; 26. byte

000230 bb22 out VIDEOPORT,video_tmp ; 0.bit first byte

000231 9525 asr video_tmp

000232 9493 inc video_ptr_l

000233 bb22 out VIDEOPORT,video_tmp ; 1.bit first byte

000234 9525 asr video_tmp

000235 ba98 out ADDRL,video_ptr_l ; output low address

000236 bb22 out VIDEOPORT,video_tmp ; 2.bit first byte

000237 9525 asr video_tmp

000238 b3d9 in video_tmp2,PINA ; load next 6 pixels :X X 5 4 3 2 1 0

000239 bb22 out VIDEOPORT,video_tmp ; 3.bit first byte

00023a 9525 asr video_tmp

00023b 0000 nop ; ========= BITSOUND (NOP) ===

00023c bb22 out VIDEOPORT,video_tmp ; 4.bit first byte

00023d 9525 asr video_tmp

00023e 0fdd lsl video_tmp2

00023f bb22 out VIDEOPORT,video_tmp ; 5.bit first byte

000240 f408 brcc pc+2

000241 21d7 and video_tmp2,mask_register

; 27.byte

000242 bbd2 out VIDEOPORT,video_tmp2 ; 0.bit second byte

000243 95d5 asr video_tmp2

000244 9493 inc video_ptr_l

000245 bbd2 out VIDEOPORT,video_tmp2 ; 1.bit second byte

000246 95d5 asr video_tmp2

000247 ba98 out ADDRL,video_ptr_l ; output low address

000248 bbd2 out VIDEOPORT,video_tmp2 ; 2.bit second byte

000249 95d5 asr video_tmp2

00024a b329 in video_tmp,PINA ; load next 6 pixels :X X 5 4 3 2 1 0

00024b bbd2 out VIDEOPORT,video_tmp2 ; 3.bit second byte

00024c 95d5 asr video_tmp2

00024d 0000 nop ; ========= BITSOUND (NOP) ===

00024e bbd2 out VIDEOPORT,video_tmp2 ; 4.bit second byte

00024f 95d5 asr video_tmp2

000250 0f22 lsl video_tmp

000251 bbd2 out VIDEOPORT,video_tmp2 ; 5.bit second byte

000252 f408 brcc pc+2

000253 2127 and video_tmp,mask_register

; 28. byte

000254 bb22 out VIDEOPORT,video_tmp ; 0.bit first byte

000255 9525 asr video_tmp

000256 9493 inc video_ptr_l

000257 bb22 out VIDEOPORT,video_tmp ; 1.bit first byte

000258 9525 asr video_tmp

000259 ba98 out ADDRL,video_ptr_l ; output low address

00025a bb22 out VIDEOPORT,video_tmp ; 2.bit first byte

00025b 9525 asr video_tmp

00025c b3d9 in video_tmp2,PINA ; load next 6 pixels :X X 5 4 3 2 1 0

00025d bb22 out VIDEOPORT,video_tmp ; 3.bit first byte

00025e 9525 asr video_tmp

00025f 0000 nop ; ========= BITSOUND (NOP) ===

000260 bb22 out VIDEOPORT,video_tmp ; 4.bit first byte

000261 9525 asr video_tmp

000262 0fdd lsl video_tmp2

000263 bb22 out VIDEOPORT,video_tmp ; 5.bit first byte

000264 f408 brcc pc+2

000265 21d7 and video_tmp2,mask_register

; 29.byte

000266 bbd2 out VIDEOPORT,video_tmp2 ; 0.bit second byte

000267 95d5 asr video_tmp2

000268 9493 inc video_ptr_l

000269 bbd2 out VIDEOPORT,video_tmp2 ; 1.bit second byte

00026a 95d5 asr video_tmp2

00026b ba98 out ADDRL,video_ptr_l ; output low address

00026c bbd2 out VIDEOPORT,video_tmp2 ; 2.bit second byte

00026d 95d5 asr video_tmp2

00026e b329 in video_tmp,PINA ; load next 6 pixels :X X 5 4 3 2 1 0

00026f bbd2 out VIDEOPORT,video_tmp2 ; 3.bit second byte

000270 95d5 asr video_tmp2

000271 fa14 bst snd_reg, 4 ; ========= BITSOUND (OP1: BIT 4) ===

000272 bbd2 out VIDEOPORT,video_tmp2 ; 4.bit second byte

000273 95d5 asr video_tmp2

000274 0f22 lsl video_tmp

000275 bbd2 out VIDEOPORT,video_tmp2 ; 5.bit second byte

000276 f408 brcc pc+2

000277 2127 and video_tmp,mask_register

; 30. byte

000278 bb22 out VIDEOPORT,video_tmp ; 0.bit first byte

000279 9525 asr video_tmp

00027a 9493 inc video_ptr_l

00027b bb22 out VIDEOPORT,video_tmp ; 1.bit first byte

00027c 9525 asr video_tmp

00027d ba98 out ADDRL,video_ptr_l ; output low address

00027e bb22 out VIDEOPORT,video_tmp ; 2.bit first byte

00027f 9525 asr video_tmp

000280 b3d9 in video_tmp2,PINA ; load next 6 pixels :X X 5 4 3 2 1 0

000281 bb22 out VIDEOPORT,video_tmp ; 3.bit first byte

000282 9525 asr video_tmp